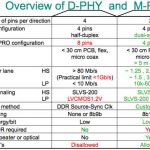

For those taking a quick look at the various MIPI Interface specification, the first reaction is to realize that they will have to look at MIPI more closely, and that it will take them longer than expected to make sure they really understand the various specifications! Let’s start with the PHY. One specification defines the D-PHY,… Read More

WEBINAR: Edge AI Optimization: How to Design Future-Proof Architectures for Next-Gen Intelligent DevicesEdge AI is rapidly transforming how intelligent solutions…Read More

WEBINAR: Edge AI Optimization: How to Design Future-Proof Architectures for Next-Gen Intelligent DevicesEdge AI is rapidly transforming how intelligent solutions…Read More WEBINAR Unpacking System Performance: Supercharge Your Systems with Lossless Compression IPsIn today's data-driven systems—from cloud storage and AI…Read More

WEBINAR Unpacking System Performance: Supercharge Your Systems with Lossless Compression IPsIn today's data-driven systems—from cloud storage and AI…Read More ChipAgents Tackles Debug. This is ImportantInnovation is never ending in verification, for performance,…Read More

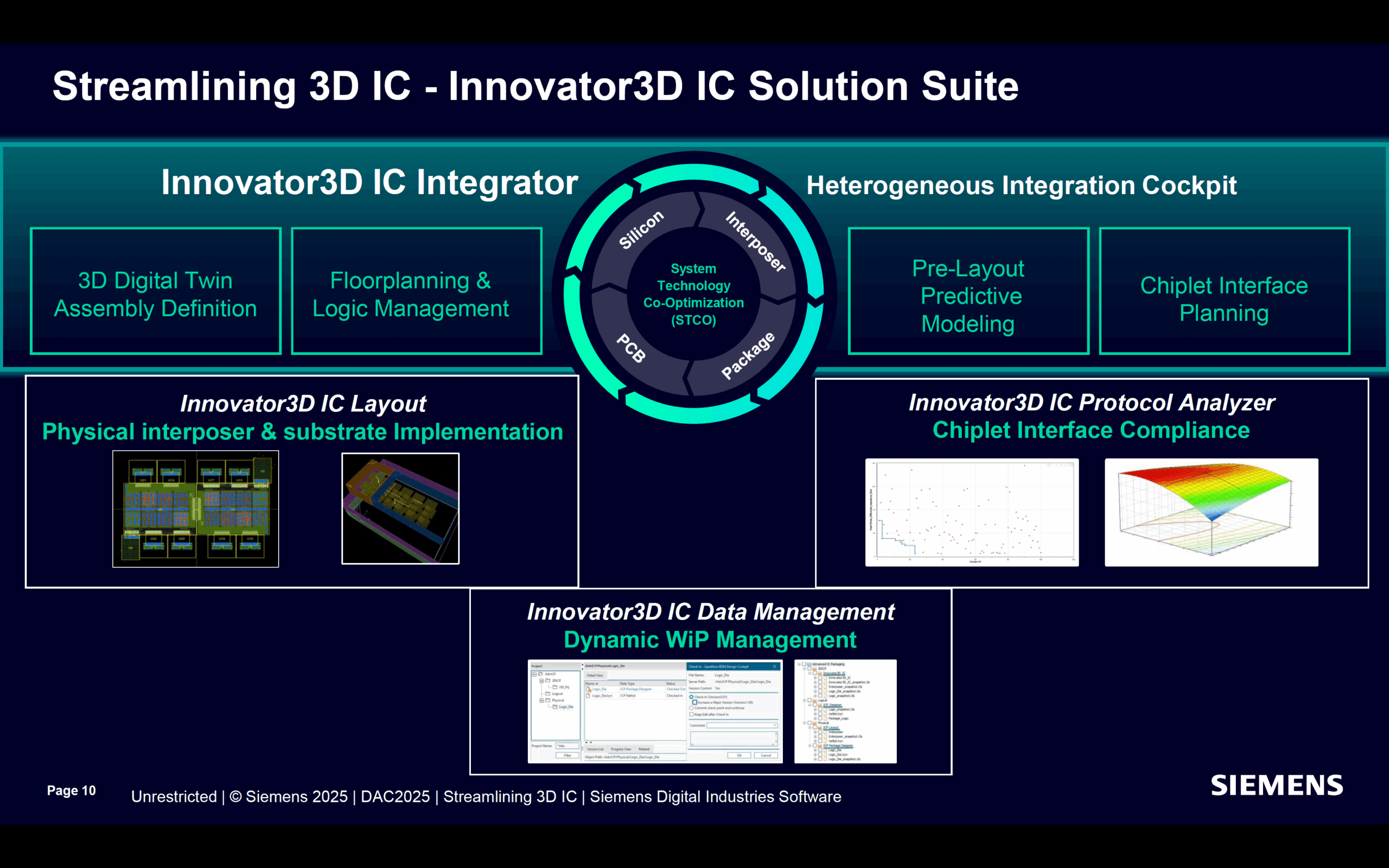

ChipAgents Tackles Debug. This is ImportantInnovation is never ending in verification, for performance,…Read More Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and AnalysisIn a major announcement at the 2025 Design…Read More

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and AnalysisIn a major announcement at the 2025 Design…Read More CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read MoreSemicon: Multiple Patterning vs EUV, round #2

Round #1 was here.

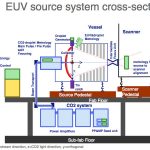

In the EUV corner were Stefan Wurm of Sematech (working on mask issues mostly) and Skip Miller of ASML who are the only company making EUV steppers (and light sources, they acquired Cymer).

You may know that the biggest issue in EUV is getting the source brightness to have high enough energy that an EUV stepper has … Read More

Constrain all you want, we’ll solve more

EDA tool development is always pushing the boundaries, driven in part by bigger, faster chips and more complex IP. For several years now, the trend has been developing tools that spot problems faster without waiting for the “big bang” synthesis result that takes hours and hours. Vendors, with help from customers, are tuning tools… Read More

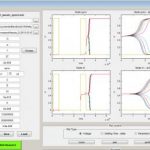

Metastability Starts With Standard Cells

Metastability is a critical SoC failure mode that occurs at the interface between clocked and clockless systems. It’s a risk that must be carefully managed as the industry moves to increasingly dense designs at 28nm and below. Blendics is an emerging technology company that I have been working with recently, their MetaACE… Read More

The FPGA Blob is Coming…

I never understood when I was a kid how ‘the Blob’ could actually catch someone but it sure did. It caught the unsuspecting, the off guard. I mean you’d have time for a soda and shower if you saw it on your road. And no, your manager is not the Blob; don’t think like that, it’s always his boss. The blob comes to consume the worker who was unaware… Read More

TSMC Q2 Results: Up 17%; 20nm and 16nm on track

TSMC announced their Q2 financial results yesterday. Revenue was $5.2B (at the high end of guidance) with net income of $1.6B. This is up 17.4% on Q1 and up 21.6% year-to-year. Gross margin is up too, at 49% which is up 3.2 points on Q1 and 0.3 points year-to-year. As usual the financial results are not directly that interesting since… Read More

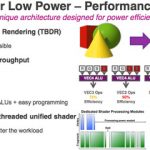

♫ IMG Sitting on the DOK of the Bay…Closin’ Timin’

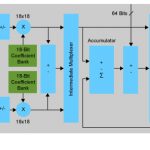

Scott Fitzgerald is supposed to have said “the rich are not like other people” to Ernest Hemingway (he didn’t). In the same way, processors are not like other blocks, and not because they have more gates (they don’t). However, special approaches to optimizing processors are important because the clock… Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

Around the World in 80 Engineers…Actually Well Over 200

Atrenta today announced Dr Ajith Pasqual, who is the Head of the Department of Electronic & Telecommunication Engineering at the University of Moratuwa in Sri Lanka (which used to be known as Ceylon) has joined Atrenta’s technical advisory board (TAB). OK, academics join EDA company’s TABs all the time so that’s… Read More

The fixed and the finite: QoR in FPGAs

There is an intriguingly amorphous term in FPGA design circles lately: Quality of Results, or QoR. Fitting a design in an FPGA is just the start – is a design optimal in real estate, throughput, power consumption, and IP reuse? Paradoxically, as FPGAs get bigger and take on bigger signal processing problems, QoR has become a larger… Read More

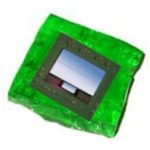

Facing the Quantum Nature of EUV Lithography