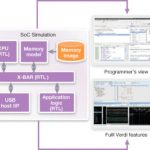

One of the big challenges with modern SoCs is that they have a complex software component as well as the hardware itself being complex. Some aspects of the hardware can be debugged independently of the software and vice versa, but often it is not immediately clear whether the source of a problem is hardware, software or some interaction… Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read MoreThe Number One ASIC Racing Team!

This weekend I was in the pits for the Flying Lizard Motorsports team at the Monterey Grand Prix. It was an auction item (donated by eSilicon) at EDA’s 50[SUP]th[/SUP] Anniversary party last year, and let me tell you it was an amazing experience and a very interesting story, absolutely. But first let me tell you that if you get a “Hot… Read More

Leveraging Design Team Energy!

Once upon a time, in 1987 to be specific, a French design team was trying to develop a 100% Made in France supercomputer. In fact, not really 100%, as the CPU chips were supposed to be made by Weitek, but we never saw any of these chips, probably too challenging to be designed right first time! Anyway, I was in charge of the design of the … Read More

Aldec is Celebrating 30 Years @ #51DAC!

Dr. Stanley Hyduke founded Aldec in 1984 and their first product was delivered in 1985, named SUSIE (Standard Universal Simulator for Improved Engineering), a gate-level, DOS-based simulator. The SUSIE simulator was priced lower than other EDA vendor tools from the big three: Daisy, Mentor and Valid (aka DMV). Today, Aldec … Read More

FD-SOI : SMIC or…Who else?

In fact, as of today, nobody can refer to an official statement made by any STM executive about name of the foundry able to process FD-SOI wafers in 28nm. We just know that the agreement is about to (or has been) signed… But we may speculate, and try to use our rational thinking. For example, the Semiwiki readers had the opportunity to… Read More

More “toddlers” innovating on the IoT

As the PC Era took shape, Tom Peters predicted the shift away from “where all the cars are parked”. He foresaw that large, established companies would no longer be the economic engine, or the dominant force in innovation. Smaller firms, even individuals, would rise to prominence in a new, technologically-driven economy.

That … Read More

Semiconductor Cost Models: Boring But Crucial

One of the most important and underrated tasks in a semiconductor company is creating the cost model. This is needed in order to be able to price products, and is especially acute in an ASIC or foundry business where there is no sense of a market price because the customer and not the manufacturer owns the intellectual property and … Read More

Eric Esteve to Present during CDN Live 2014 in Munich

I will have the privilege to give an “IP Outlook” presentation during next Cadence event in Europe, CDN-Live to be held in Munich the 19[SUP]th[/SUP] to 21[SUP]st[/SUP] of May. I had a look at the agenda, and the conference will be pretty busy, especially on Tuesday, as there will be more than fifty presentations, starting at 10:30… Read More

What Do You Do When You Are Not Designing?

DAC is coming up in a month (OMG less than 4 weeks and we are so not ready I hear a hundred marketing people cry out). That gives you four weeks (and a couple of days) to tell Mentor what you do in your spare time that you are passionate about (spare time, I hear a hundred engineers cry out, what is that?) and you could win $300.

For DAC, Mentor… Read More

FD-SOI Not Just For France Any More, China Signs On?

The COO of ST Microelectronics, Jean-Marc Chery announced that they have signed a new foundry agreement for FD-SOI. What he actually said doesn’t reveal who the foundry in question is:“We have just signed a strategic agreement with a top-tier foundry for 28nm FD-SOI technology. This agreement expands the ecosystem, assures… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!