Let’s start with apologies: when guessing that SMIC would be the 2[SUP]nd[/SUP] source foundry for ST-Microelectronics 28nm FD-SOI, I was wrong. To be honest, if I had made the assumption that Samsung was this double source, I would have generated dozen of comments, calling me “crazy blogger”…for the best. Announcing Samsung… Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read MoreAtmel and the Arduino Zero

As I wrote about last month, this weekend is the Maker Faire in San Mateo. If you are interested in the cutting edge of what people are getting up to outside of the corporate world, this is the place to go. You will see stuff that you will not hear about for a year or two when it finally goes mainstream.

Increasingly, there is a lot of electronics… Read More

Apache Design @ #51DAC Must See!

Register to hear industry experts from top semiconductor companies share their best practices that enable the next generation of high-performance, low power designs for mobile, automotive and other applications. Meet our technologists for in-depth presentations, case studies and demos on the industry’s leading simulation… Read More

Synopsys @ #51DAC Must See!

Accelerating Innovation—that has been at the heart of Synopsys’ commitment to its customers for more than 25 years. As a leader in EDA and semiconductor IP, Synopsys’ software, IP and services help engineers address their design, verification, system and manufacturing challenges and accelerate their innovations. Since 1986,… Read More

Samsung Endorses FD-SOI!

This is probably one of the biggest stories we will cover this month, if not this year, absolutely. In partnership with STMicroelectronics, Samsung will manufacture 28nm FD-SOI chips for the fabless semiconductor community starting now. This proves without a shadow of a doubt that Samsung is serious about the foundry business.… Read More

Cadence @ #51DAC Must See!

Cadence is excited to bring a full slate of demos, technical presentations, papers, and more to the Design Automation Conference (DAC) June 1-5, 2014, in San Francisco, CA. From our technical experts, you’ll learn tips and techniques from areas including low power, mixed signal, advanced nodes, signoff, verification, and IP,… Read More

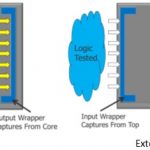

Taming The Challenges of SoC Testability

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More

A Brief History of the Apple MacBook Pro

I’m typing this blog today with my trusty Apple MacBook Pro – a 17″ laptop with matte display and 16GB of RAM, but don’t stereotype me as an Apple fanboy because I also own the fantastic Samsung Galaxy Note II phone (aka phablet). Some industry pundits would have us believe that desktops and laptops are going… Read More

A Brief History of MunEDA

In 2002, MunEDA was launched under the guidance of EDA academic veterans and IEEE fellows Prof. Kurt Antreich and Prof. Helmut Gräb (TUM Munich Technical University ) which represented 20 plus years of EDA research and experience. All MunEDA tools are combined in a tool suite called WiCkeD[SUP]TM[/SUP]. The tool suite brand was… Read More

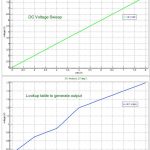

Teach Yourself Silvaco

In the dim and distant past, if you wanted to learn how to use a particular EDA tool then you would go on a training course. This would often be multiple days and often a significant dollar investment too. For most EDA companies, that option still exists and the big 3 have quite extensive training catalogs.

But nowadays it is often easier… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era