One of the things that eSilicon does is handle all the backend operations for the designs that they do. eSilicon is a fabless ASIC company and so the most visible part of the business is the design (not to mention IP which is a critical input into design these days). But another key part is arranging with foundries like TSMC to get the … Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreCadence Go (war-game) strategy

I was attending to CDN-Live in Munich last week, so I was expecting Cadence to announce new IP related acquisition like Lip-Bu Tan did last year (Cosmic Circuit, Evatronix and Tensilica). In fact, Lip-Bu was not in Munich and Charlie Huang, SVP Worldwide Field Operations and System & Verification Group, was holding the morning… Read More

IBM and GLOBALFOUNDRIES Deal!

An interesting deal was announced last week, another piece in the What is Next for GlobalFoundries? puzzle. IBM is sending up to 200 employees from their East Fishkill R&D facility to GF’s Malta R&D center in Saratoga County. The first thing that comes to my mind is 10nm! Considering GF is licensing Samsung 14nm, what else… Read More

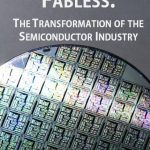

Fabless Book Giveaway at #51DAC!

The generosity of the fabless semiconductor ecosystem never ceases to amaze me. Paul McLellan and I wrote a book for the greater good and now key members of our industry will make sure that 1,500 people at this year’s Design Automation Conference will get copies. As a special thank you to all of our supporters SemiWiki will be hosting… Read More

GlobalFoundries Gets a New Manager in NY

GlobalFoundries is on the move. Of course the biggest announcement recently was the licensing of Samsung’s process to run in fab 8 in Malta, New York. This means that fab 8 will be a viable alternative, a true second source for Samsung production and one that doesn’t compete with its customers as Samsung does in many … Read More

EUV Will Never Happen

I had lunch today with a guy who has to remain nameless. But he is on the edge of the semiconductor lithography thing. He told me EUV will never happen. Of course lots of people have said that. Me for one. But he said everyone knows it. The investment community, the foundries, everyone. Intel put money into ASML in the hopes that it would… Read More

A Novel Approach to IC Design in the Cloud

Migration to cloud computing for scientific and engineering applications is inevitable. More specifically for IC design, the benefits are significant:

- Common IC design infrastructure to unburden each user from setting up and maintaining a separate infrastructure

- Cloud based IC design enables global collaboration among

More Moore or No More?

Moore’s is still the law, and device scaling remains the key focus of front-end process research, however next-generation technologies–and the Big Data, cloud computing world that supports mobile, IoT, and other next-gen applications–are the new drivers, bringing new demands and challenges running … Read More

Motley Fools Intel Investors Again!

It really is quite a racket. Investor bloggers spread semiconductor disinformation for $.01 per click, that coincidentally covers their stock positions, and I get paid $300 per hour to explain it to Wall Street. While I appreciate the opportunity to bond with the financial people, I do wonder how these bloggers sleep at night.… Read More

Variation-Aware Custom IC Design Best Practices

I’ve worked with Solido for 5 years, and it’s been a pleasure to watch the world’s top semiconductor companies and foundries adopt Solido software for their SPICE simulation flows.

Sub-28nm design starts are accelerating, growing from 150 in 2012 to 900 this year. The move to sub-28nm design nodes is being driven by consumer electronic… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center