When we talk about parasitic, we talk about post layout design further expanded in terms of electrical components such as resistances and capacitances. In the semiconductor design environment where multiple parts of a design from different sources are assembled together into highly complex, high density SoC, imagine how complex… Read More

ChipAgents Tackles Debug. This is ImportantInnovation is never ending in verification, for performance,…Read More

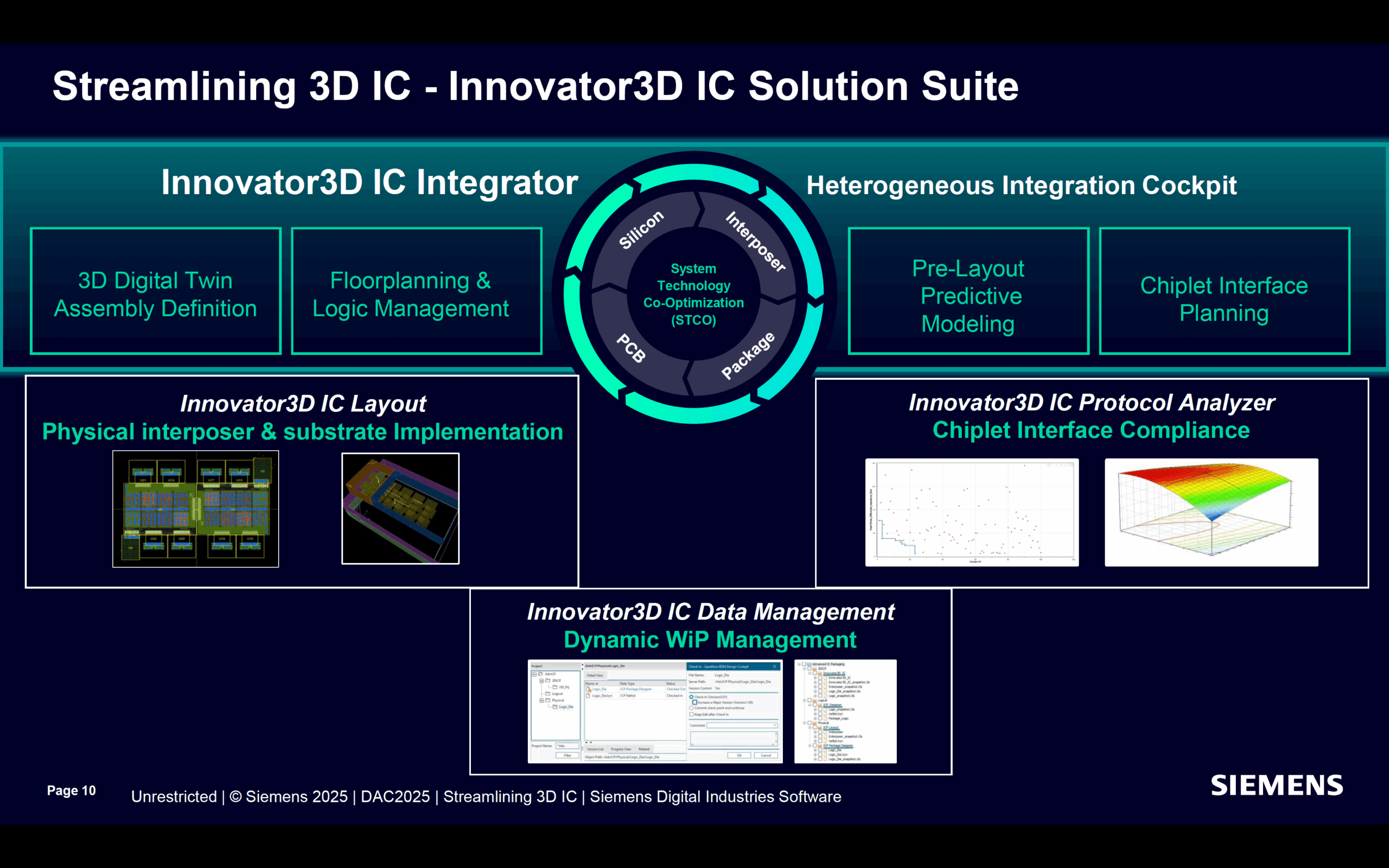

ChipAgents Tackles Debug. This is ImportantInnovation is never ending in verification, for performance,…Read More Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and AnalysisIn a major announcement at the 2025 Design…Read More

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and AnalysisIn a major announcement at the 2025 Design…Read More CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More Rethink Scoreboards to Supercharge AI-Era CPUsBy Dr. Thang Minh Tran, CEO/CTO Simplex Micro…Read More

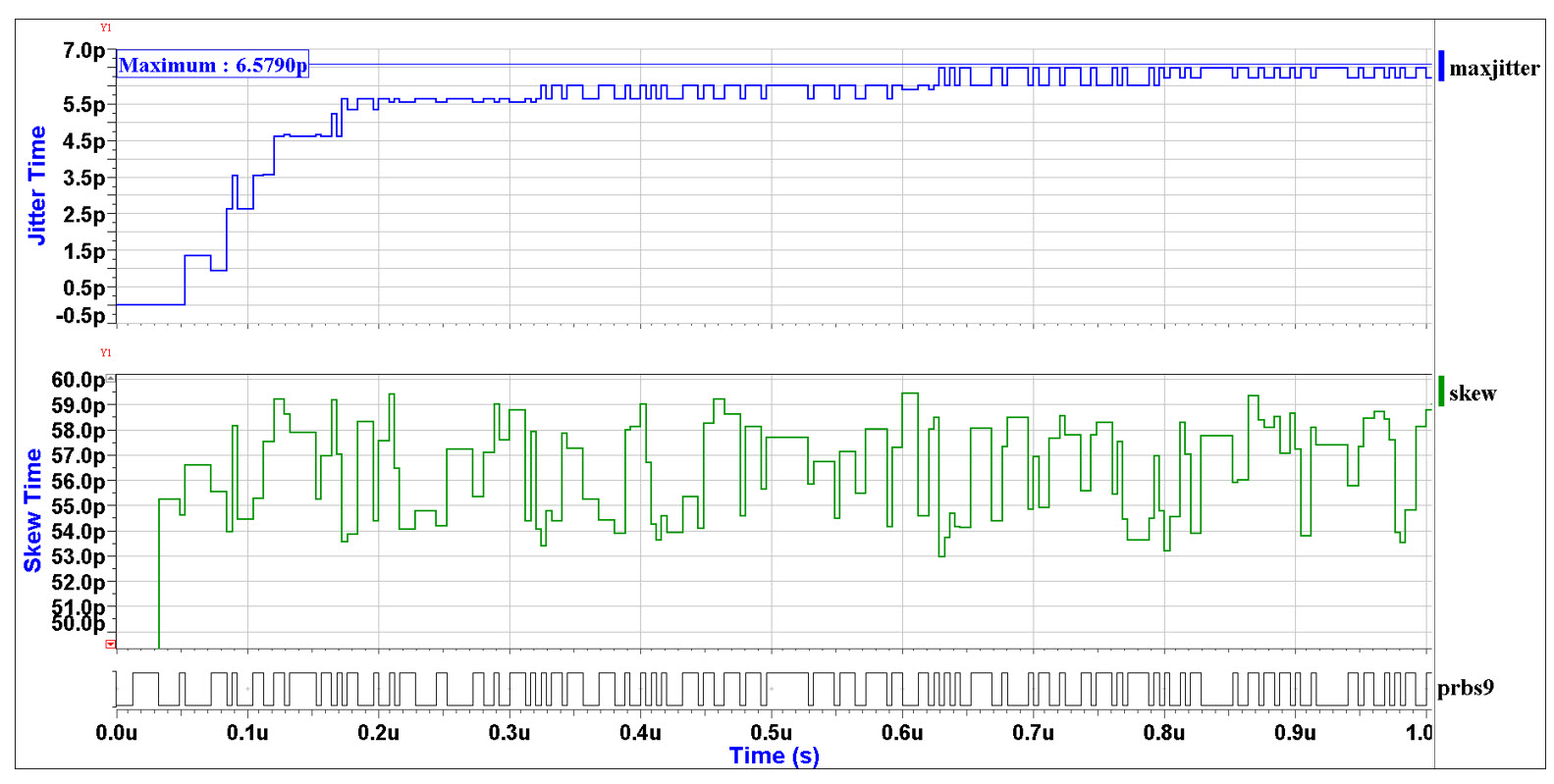

Rethink Scoreboards to Supercharge AI-Era CPUsBy Dr. Thang Minh Tran, CEO/CTO Simplex Micro…Read More Jitter: The Overlooked PDN Quality MetricBruce Caryl is a Product Specialist with Siemens EDA…Read More

Jitter: The Overlooked PDN Quality MetricBruce Caryl is a Product Specialist with Siemens EDA…Read MoreRekeying the IoT with eMTP

For non-volatile storage in IoT devices, there is technology designed to be reprogrammed many times, and technology designed to be programmed once. The many times mode is for application code, while the once mode is for keying and calibration parameters. We are about to enter the IoT rekeying zone, in between these two extremes.… Read More

Wearables the Big Hit at CES

There were a number of trends discernible at CES this year, one of the big ones being wearables, especially in the medical and fitness areas. I wear a FitBit Flex and I have, but rarely wear, a Pebble Watch that links to my iPhone. I would say that at this point they are promising but are more gimmicks than truly useful. My Fitbit measures… Read More

Dan Niles: Strong Developed Markets, Weak Emerging

Yesterday was Dan Niles’s economic review that he presents quarterly for GSA. As always he starts from big macroeconomic picture and ends up looking at the implications for semiconductor end-markets and thus the implication for semiconductors in general and the fabless ecosystem in particular.

The big picture is that… Read More

ESD at TSMC: IP Providers Will Need to Use Mentor to Check

I met with Tom Quan of TSMC and Michael Beuler-Garcia of Mentor last week. Weirdly, Mentor’s newish buildings are the old Avant! buildings where I worked for a few weeks after selling Compass Design Automation to them. Odd sort of déja vu. Historically, TSMC has operated with EDA companies in a fairly structured way: TSMC … Read More

Have you Tried ALDEC?

I must admit. I was too comfortable. Let me explain, I’m a ModelSim guy from Mentor Graphics. I did not really think nor care much of the other RTL simulator options. How could someone build a better tool with respect to simulation? Let me introduce you to Aldec. Aldec was founded in 1984 by Dr. Stanley M. Hyduke. 30 years later they are… Read More

Just Released! Fabless: The Transformation of the Semiconductor Industry

The book “Fabless: The Transformation of the Semiconductor Industry” is now available in the Kindle (mobi) and iBooks (ePub) formats. We are really looking forward to your feedback before we go to print in March. This was truly a Tom Sawyer experience for me. As the story goes Tom made whitewashing a fence seem like fun so his friends… Read More

A Power Optimization Flow at the RTL Design Stage

SoC designers can code RTL, run logic synthesis, perform place and route, extract the interconnect, then simulate to measure power values. Though this approach is very accurate, it’s also very late in the implementation flow to start thinking about how to actually optimize a design for the lowest power while meeting all… Read More

TSMC Responds to Intel’s 14nm Density Claim!

TSMC responded to Intel’s 14nm density advantage claim in the most recent conference call. It is something I have been following closely and have written about extensively both publicly and privately. Please remember that the fabless semiconductor ecosystem is all about crowd sourcing and it is very hard to fool a crowd of semiconductor… Read More

Semiconductor IP and Correct-by-construction Workspaces

SoC hardware designers could learn a thing or two from the world of software development, especially when it comes to the topic of managing complexity. Does that mean that hardware designers should literally use a software development environment, and force fit hardware design into file and class-based software methodologies?… Read More

Facing the Quantum Nature of EUV Lithography