As a professional conference attendee I see a direct correlation between the number of people attending and the quality of the keynotes. Let’s face it, it’s all about the keynotes so you had better get some big names if you want more than your friends and family to show up. In this regards the upcoming CASPA event will probably be one… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreBouncing Between iPhone and Android

I’ve now been the proud owner of a Motorola Droid, HTC Incredible, iPhone 5, Samsung S4 and iPhone 6. I just can’t decide if I’m in the iPhone or Android camp!

If you don’t feel like reading the entire article, the iPhone 6 is a superior phone experience (judgement made on my 3 weeks of ownership). If you are… Read More

WTL Leverage FDSOI to Achieve Both Low Power AND High Speed

In fact, this is the title of a presentation given by Pete Foley during FD-SOI Forum 2014 held in Shanghai, a couple of weeks ago. What is nice with clever people like Pete Foley is that they get the point, and get it quickly. Getting the point is to insert AND in capital in the title, as using FD-SOI technology allows to benefit from low-power… Read More

Samsung Profits Fall 60%

Samsung’s profits fell to $3.8B which is 60% down on where they were a year ago. They said this is primarily due to a shortfall in smartphone sales. Samsung’s problem is not that it competes with Apple, their phones seem close enough that the Galaxy line has been doing very well in places like the US. It’s problem… Read More

Intel Invades China Mobile Market!

As you may have heard, Intel is making some interesting moves into the China mobile market. At first it had me a bit puzzled but I had some lengthy discussions about it during ARM TechCon last week so I’m ready to start writing. Spoiler alert: This will be pro Intel so please sit down and take some deep breaths before reading.

The first… Read More

Silicon Does NOT Lie!

In the 30+ years that I have worked in Silicon Valley I have seen many great products fail and even more mediocre products succeed, the difference being how the companies communicate to the outside world. In the semiconductor industry, presenting the value proposition of your company or product is under even more scrutiny now that… Read More

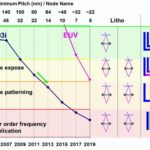

10nm, the View from IBM

On the Cadence booth at DAC, Lars Liebmann of IBM presented on the challenges of 10nm. As he put it, how the lithography folks are keeping things very interesting for the EDA tool development engineers. Although 14nm/16nm hasn’t yet ramped into HVM, the advanced work for tools and IP has all moved to 10nm. Although Lars gave… Read More

The Apple Samsung TSMC Intel 14nm Mashup!

One of the strengths of the fabless semiconductor ecosystem is competition since it keeps innovation high and prices low. One of the challenges of fostering competition is that you have to make good on a threat of using a competing product during a pricing negotiation. Well, in my opinion, for the next version of the iPhone, Apple… Read More

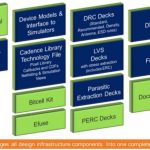

Key Collaboration to Enable Designs at Advanced Nodes

In the semiconductor ecosystem, several partners (or better to say stakeholders) join together in the overall value chain to finally output the most coveted chip, err I should say SoC these days. It becomes really interesting when we start analyzing the real value added by each of them, none appears to be less. Well, then to whom … Read More

GlobalFoundries and Samsung at ARM

It was back in April that GlobalFoundries and Samsung announced that GF would license Samsung’s 14nm process to run in their Fab8 in upstate New York. Since then there has not really been any news and of course those of us that follow the foundry industry wondered to what extent there was real substance to the agreement or if … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center