Cliff Hou had two major appearances at DAC this year. He gave the opening day keynote…and he wrote the forward to Dan and my bookFabless: the Transformation of the Semiconductor Industry which about 1500 lucky people got a copy of courtesy of several companies, most notably eSilicon who sponsored the Tuesday evening post-conference… Read More

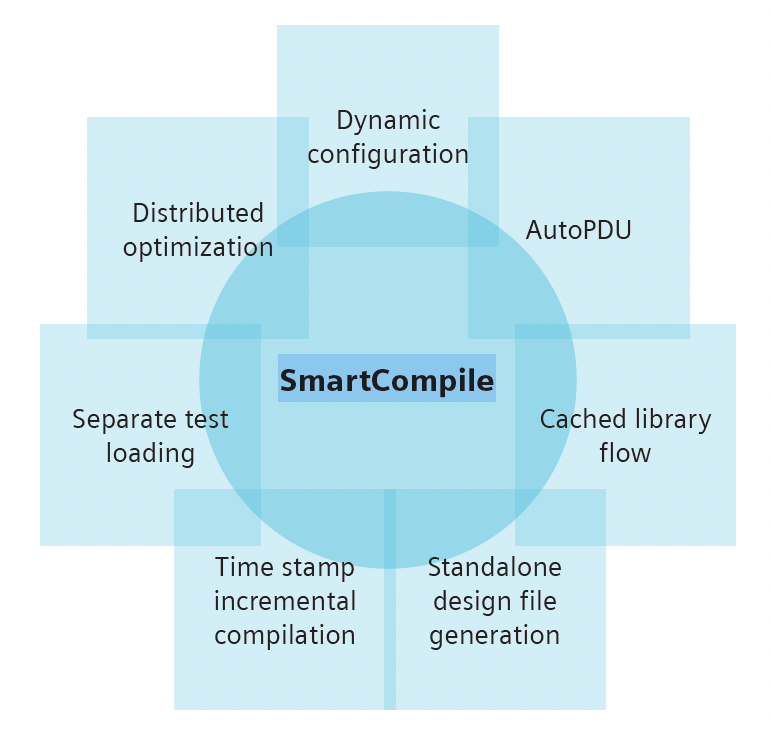

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC VerificationIn the race to deliver ever-larger SoCs under…Read More

Revolutionizing Simulation Turnaround: How Siemens’ SmartCompile Transforms SoC VerificationIn the race to deliver ever-larger SoCs under…Read More Arteris Simplifies Design Reuse with Magillem PackagingMany know Arteris as the “network-on-chip”, or NoC,…Read More

Arteris Simplifies Design Reuse with Magillem PackagingMany know Arteris as the “network-on-chip”, or NoC,…Read MoreThe Secret Essence of an IoT Design

Today the semiconductor industry along with electronics industry is looking up to capitalize from massive expansion foreseen in IoT (Internet of Things) domain. In simple terms we can consider IoT as connectivity between machines which can communicate with each other and work as programmed. In localized applications such … Read More

Intel Invests in the Fabless Ecosystem!

During my illustrious career one of the most useful axioms that I use just about everyday day is: “Understand what people say but also understand why they are saying it.” This certainly applies to press releases so let’s take a look at what Intel unleashed during #51DAC (in alphabetical order):

ANSYS And Intel Collaborate… Read More

ARC EM DSP supports Always-on Devices

The ARC EM family is the low-power, embedded and low footprint processor part of the larger ARC processor. To target the ultra low-power markets like wearable and IoT, Synopsys has added DSP capabilities to EM5D and EM7D. To be specific, these cores are optimized for ultra low-power control and DSP, thanks to:

- Energy-efficient

Enabling Technologies that Will Shape the next Wearables

One of the benefits of spending the last 30 years working in Silicon Valley and publishing a fabless semiconductor book is that I get invitations to speak at events I would normally be attending. Being on the other side of the podium is truly a unique experience and one worth pursuing, absolutely. This month I spoke at #51DAC about … Read More

Noise-Coupled Analysis for Automotive ICs at DAC

My favorite method to learn about EDA tools at DAC is by listening to actual IC designers, so on June 3rd I heard Jacob Bakker from NXP talk about his experience with noise coupled analysis for advanced mixed-signal automotive ICs.… Read More

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

On the Road from Makers to Consumers

It’s time to break with conventional thinking. For decades, the measure of success for semiconductors has been OEM design wins. Most consumers haven’t known, or cared, about what is inside their electronic gadgets, as long as they work. That may be about to change, because a new intermediary is finding its voice – and being… Read More

Workshop: Embedded Applications and Kernels

Design Automation Conference Workshop on Suite of Embedded Applications and Kernels

In June, the first Suite of Embedded Applications and Kernels, or SEAK, workshop at the 2014 Design Automation Conference in San Francisco introduced a new Defense Advanced Research Projects Agency program in the area of embedded system benchmarking… Read More

A Brief History of QuickLogic

Quicklogic was founded in 1988 as a fables semiconductor company supplying anti-fuse devices. In fact VLSI Technology, where I was working at the time, was their foundry.

Although today anti-fuse is often used as a generic word for one-time-programmability, the origins of the name are grounded in reality. In a fuse, like the things… Read More

Moore’s Law Wiki