Recently Intel and Micron announced a new three dimensional cross point (3D Xpoint) memory. The 3D Xpoint announcement has generated a lot of questions and interest in what this new memory is and where it may fit in the semiconductor market. … Read More

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More

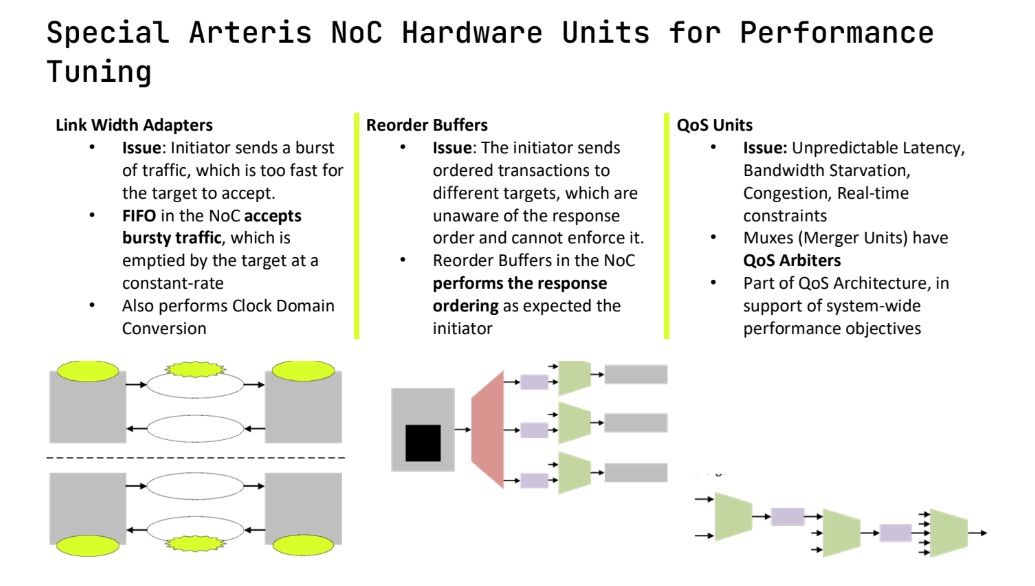

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More

NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More From Wooden Boards to White Gloves: How FPGA Prototyping and Emulation Became Two Worlds of Verification… and How the Convergence Is UnfoldingFPGA prototyping and hardware emulation originated from two…Read More

From Wooden Boards to White Gloves: How FPGA Prototyping and Emulation Became Two Worlds of Verification… and How the Convergence Is UnfoldingFPGA prototyping and hardware emulation originated from two…Read More When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read MoreHow to Overcome NoC Validation Multiple Challenges?

NetSpeed has developed NocStudio, a front end optimization design tool helping architects to create SoC architecture bridging the gap with the back end, floor planning and place and route. At the chip level, NocStudio generates a cache-coherent Network-on-Chip (NoC) allowing interconnecting the various CPU, GPU or Acceleration… Read More

All Models Are Wrong, Some Are Useful

“All models are wrong, some are useful.” This remark is attributed to the statistician George Box who used it as the section heading in a paper published in 1976.

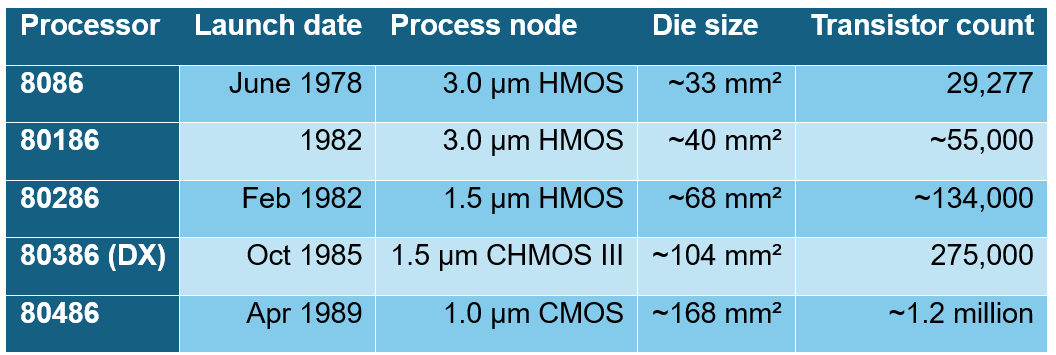

Just for fun I looked up a few semiconductor statistics from 1976. Total capital spending was $238M in Japan and $306M in US and…that’s it, there was nobody else back then … Read More

Mongoose: The Making of Samsung’s Custom CPU Core

Samsung is seemingly ready to move to a new milestone in its brief but exciting system-on-chip (SoC) history: a custom CPU core codenamed Mongoose. It’s going to be based on ARMv8 instruction set and is expected to outperform the Exynos 7420 application processor that Samsung unveiled this year. There are some media reports… Read More

Thermal Reliability and Power Integrity for IC Design

When I designed DRAM chips at Intel back in the 1970’s we didn’t really know what the die temperature would be before taping out silicon, instead we waited for packaged parts to come back and then did our thermal measurements. IC designers today don’t have that luxury of taping out their new SoC without having … Read More

Replacing the British Museum Algorithm

In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

FDSOI As a Multi-Node Platform

One of the main criticisms of the FDSOI technology has been that it is a one-node solution at best and is not scalable to the future. Such arguments are typically based on the “gate-length-scaling” assumptions which do not capture the past and current trends of the CMOS technology as I discussed in my earlier post. Back in the early… Read More

Apple’s Butterfly Effect?

The Butterfly Effect (chaos theory) describes how small changes to complex systems can result in large unforeseen consequences over time. The Apple Effect describes how a once struggling computer company completely disrupted a dozen different industries including semiconductors. Apple is now the largest and most influential… Read More

eSilicon Truly Puts the ‘e’ in Silicon

eSilicon have a new website. Companies update their websites regularly, so why is this news? Well, eSilicon increasingly does their business on the web. They are not like Facebook, say, where their business is entirely web-based, there is a physical business behind them. So they are more like Lyft for chips. Obviously Lyft requires… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint