The recent teardowns of Samsung Galaxy S6 smartphone have one thing written all over them: Samsung is doubling down on its logic business. Although most of the technology press coverage went to Exynos 7420, the first mobile SoC manufactured at the 14nm FinFET process, Samsung’s other logic chips inside the S6 handset equally… Read More

Arteris at the 2025 Design Automation Conference #62DACKey Takeaways: Expanded Multi-Die Solution: Arteris showcases its…Read More

Arteris at the 2025 Design Automation Conference #62DACKey Takeaways: Expanded Multi-Die Solution: Arteris showcases its…Read More Secure-IC at the 2025 Design Automation Conference #62DACSecure-IC at DAC 2025: Building Trust into Tomorrow’s…Read More

Secure-IC at the 2025 Design Automation Conference #62DACSecure-IC at DAC 2025: Building Trust into Tomorrow’s…Read More The Sondrel transformation to Aion SIlicon!Ollie is a commercially astute senior leader with…Read More

The Sondrel transformation to Aion SIlicon!Ollie is a commercially astute senior leader with…Read More Keysight at the 2025 Design Automation Conference #62DACKeysight Showcases AI-Ready EDA and Multi-Physics Innovation at…Read More

Keysight at the 2025 Design Automation Conference #62DACKeysight Showcases AI-Ready EDA and Multi-Physics Innovation at…Read More Infinisim at the 2025 Design Automation Design Conference #62DACClock Matters: What Infinisim Is Showcasing at DAC…Read More

Infinisim at the 2025 Design Automation Design Conference #62DACClock Matters: What Infinisim Is Showcasing at DAC…Read MoreTCAD Enables Moore’s Law to Continue

We live in very interesting times, you can wear an Android watch from Samsung that uses 14 nm FinFET technology, attend the 52nd DAC conference in June to learn about EDA and IP vendors supporting FinFET, and read about research work for new devices down to 5 nm. TCAD is that critical software technology that enables the development… Read More

TSMC 10nm Readiness and 3DIC

At the TSMC Technology Symposium last month Suk Lee presented a lot of information on design enablement. Suk is an interesting guy with a unique background in ASIC, Semiconductor, EDA, and now Foundry. In baseball terms that would be like playing infield, outfield, home plate, and umpire!

Around the turn of the millennium Suk actually… Read More

Crossing the Chasm: From Technology to Valuable Enterprise

One of the advantages of being an independent consultant is that I get to choose who I work with and what type of projects I accept. In fact, that is why I originally started blogging, to get exposure to a wide range of topics and brand myself as a strategic semiconductor business development professional. Now rather than wasting time… Read More

Why Intel will Never Succeed in IoT Market?

Let me precise that by “IoT” I think about the IoT devices market, made of hundreds of application, wearable gadget to medical, home automation, and so on. One direct consequence of IoT (device) market explosion will be the strong growth of the server market (cloud), to transfer, compute and store information generated by the billions… Read More

Fractal at DAC 2015 – What’s new?

I have been observing Fractal Technologiesexhibiting at DACyear after year, and every year they have demonstrated good value added features in their tools for SoC and IP development. This year at 52[SUP]nd[/SUP] DAC Fractal’s booth number is 1110. Earlier in this year Fractal had added a new ‘Cdiff’ feature in its flagship product… Read More

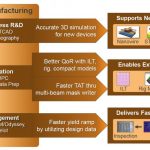

ASMC 2015 Preview

From May 3[SUP]rd[/SUP] to May 6[SUP]th[/SUP] the 26[SUP]th[/SUP] annual Advanced Semiconductor Manufacturing Conference (ASMC) will be held in Saratoga Springs, New York.

The ASMC offers a unique view of challenges to the semiconductor industry focusing on things like defect reduction, metrology and fab operations. In… Read More

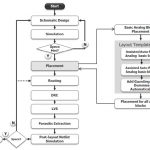

Can You Really Automate Analog IC Layout?

Digital IC design has been largely automated with high-level languages, RTL coding, logic synthesis, and automated place and route tools. What about analog IC layout automation, is it possible? A few EDA companies think that it is possible and even practical. In recent memory there were two companies really focused on analog … Read More

Extending Moore in Silicon

A year ago many eulogized the death of Moore’s Law at 28nm due to higher prices per transistor at more advanced nodes, but now that we have celebrated the 50th anniversary let’s look ahead to technology scaling and electronic systems miniaturization for the next decade. Despite our industry’s bipolar tendencies and daunting technical… Read More

Single Chip MCU + DSP Architecture for Automotive: SAMV71

It’s all about Cost of Ownership (CoO) and system level integration. If you target automotive related application, like audio or video processing or control of systems (Motor control, Inverter…) you need to integrate strong performance capable MCU with a DSP. In fact if you expect your system to support Audio Video Bridging (AVB)… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot