Intel has been the focus of a lot of attention in the last week due to the company’s major restructuring announcement which came on the heels of Intel’s most recent earnings announcement. The majority of analyses that immediately followed the company’s announcement focused singularly on the layoffs, which amount to 11% of the … Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

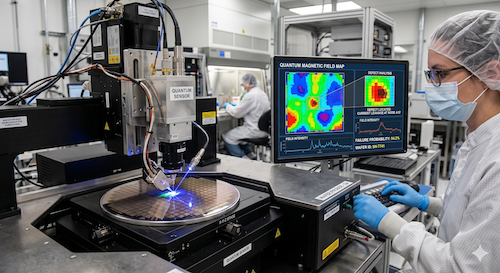

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read MoreHighlights of the 28nm FD-SOI San Jose Presentations

Most of the presentations from the FD-SOI Symposium in San Jose last month (April 2016) are now available on the SOI Consortium website (click here to see the full list — if they’re posted, you can download them freely from there). If you don’t have time to wade through them all, here are some of the highlights. … Read More

Facebook and Deep Reasoning with Memory

Neural nets as described in many recent articles are very capable at recognizing objects and written and spoken text. But like anything we can build, or even imagine, they have limitations. One problem is that after training, the neural nets we usually encounter are essentially stateless. They can recognize static patterns but… Read More

Electrostatic Discharge analysis of FinFET technology

Sofics recently had the opportunity to characterize FinFET technology through cooperation with one of its customers. We analyzed the technology related to ESD and identified several challenges.… Read More

Free Webinar: Designing Low-Power IoT Systems

As I have written before, IoT looks to be a key driver for design starts and future semiconductor revenue growth which is why we wrote “PROTOTYPICAL” and included a field guide to FPGA Prototyping. If you want to get funding for your new IoT chip project, having a working prototype is a good thing, absolutely. If you want to take a look… Read More

My #53DAC Must See List!

It may be hard to believe but this happens to be my thirty third Design Automation Conference. Where does the time go? Three of my kids are out of college and the last one is getting close. That is where my time has gone. The conference itself started in 1964 but my first one was in 1984 in Albuquerque, New Mexico. In fact, that was the year… Read More

A Shot in the ARM for IoT

I recently attended the IoT Developers Conference in Santa Clara, CA. There were clearly two major themes in the talks – security and low power. The volume market in IoT is in the edge node devices. These devices have two important characteristics. They acquire data which needs to be transmitted and they typically are battery-driven… Read More

Reusable HW/SW Interface for Portable Stimulus

Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

IMEC Technology Forum (ITF) – Moving the Electronics Industry Forward

IMEC is a technology research center located in Belgium that is one of the premier semiconductor research centers in the world today. The IMEC Technology Forum (ITF) is a two-day event attended by approximately 1,000 people to showcase the work done by IMEC and their partners.

Gary Patton is the Chief Technical Officer and Senior… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior