The GSA US Executive Forum is in its 5[SUP]th[/SUP] year. It is a time for top level semiconductor executives to meet and try to make sense of a very complex and fast moving industry that has tremendous influence on modern day life. You can see a list of attendees with bios and pictures HERE. There is a lot to talk about (The Future of Drones… Read More

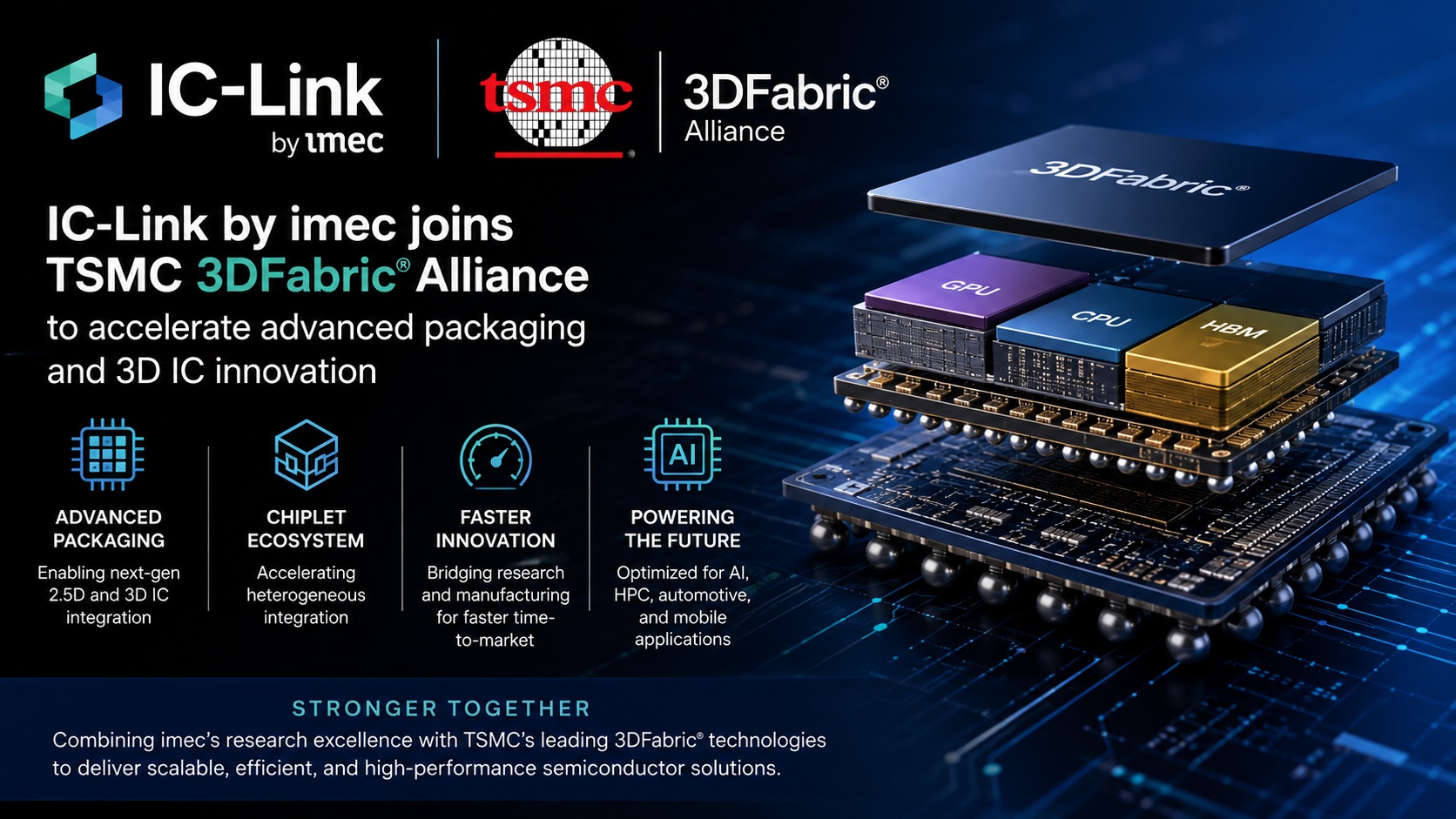

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read MoreeSilicon Just Made It Easier to Explore Memory Tradeoffs

If you are building an advanced SoC, you know that you’re going to need a lot of embedded memory. Unless this is your first rodeo, you also know that which memories you choose can have a huge impact on Power, Performance and Area (PPA) and, for some applications, Energy (power integrated over time), Temperature and Reliability. Which… Read More

Circuit Simulation Videos Show How To

One of the things that I miss most about attending trade shows like DAC in the old days was that you actually got to see EDA tools being demonstrated live in the exhibit area. You could see what the GUI looked like, how the dialogs worked, and learn what kind of control you could have during analysis. Most of what you see today at DAC in the… Read More

CEO Interview: Marie Semeria of LETI

Laboratoire d’électronique des technologies de l’information (LETI) is a French research center, affiliate to the CEA (Commisariat a l’Energie Atomique). Since LETI creation in 1967, this affiliation has two consequences, the money was flowing from the deep pocket of the atomic industry to sustain advanced … Read More

Machine Learning – Turning Up the Sizzle in EDA

There’s always a lot of activity in EDA to innovate and refine specialized algorithms in functional modeling, implementation, verification and many other aspects of design automation. But when Google, Facebook, Amazon, IBM and Microsoft are pushing AI, deep learning, Big Data and cloud technologies, it can be hard not to see… Read More

Case study illustrates 171x speed up using SCE-MI

As SoC design size and complexity increases, simulation alone falls farther and farther behind, even with massive cloud farms of compute resources. Hardware acceleration of simulation is becoming a must-have for many teams, but means more than just providing emulation… Read More

Do You Know the (Green) Wave in San Jose?

No. A green wave isn’t something you do at a New York Jets or a Michigan State Spartans game. A green wave is that thing your dad or obsessive friend or maybe YOU do when you try to synchronize your driving with the changing of sequential traffic lights.

Connected Signals, BMW and Argonne National Lab are kicking off a study in … Read More

Robots could eventually replace soldiers in warfare. Is that a good thing?

The United States has on its Aegis-class cruisers a defense system that can track and destroy anti-ship missiles and aircraft. Israel has developed a drone, the Harpy, that can detect and automatically destroy radar emitters. South Korea has security-guard robots on its border with North Korea that can kill humans.

All of these… Read More

SOC Design Techniques that Enable Autonomous Vehicles

Robots – we have all been waiting for them since we were young. We watched Star Wars, or in the case of the slightly longer-lived of us, we watched Forbidden Planet or Lost in Space. We knew that our future robot friends would be able to move around and interact with their environment. What we did not foresee long ago was that instead of… Read More

‘Que Legal,’ Uber é Legal

Uber went live in Florianopolis on September 30, a week before my wife and I arrived for some down time. But rumors suggested that the service was shuttered almost as soon as it started with a couple of drivers detained and their vehicles impounded. The word was spreading that the service was considered illegal.

As fate would have … Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting