Any sufficiently advanced technology is indistinguishable from magic, as the saying goes. Which is all very well when the purpose is entertainment or serving the arcane skills of a select priesthood, but it’s not a good way to grow a market. Then you want to dispel the magic aura, make the basic mechanics more accessible to a wider… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreMargin Call

A year ago, I wrote about Ansys’ intro of Big Data methods into the world of power integrity analysis. The motivation behind this advance was introduced in another blog, questioning how far margin-based approaches to complex multi-dimensional analyses could go. An accurate analysis of power integrity in a complex chip should… Read More

Memory drives semiconductor boom in 2017

The semiconductor market was down 0.4% in first quarter 2017 from 4Q 2016 and up 18.1% from a year ago, according to World Semiconductor Trade Statistics (WSTS). The 0.4% decline in 1Q 2017 versus 4Q 2016 is strong compared to an average 4% decline from 4Q to 1Q over the previous five years. The relative strength in 1Q 2017 was driven… Read More

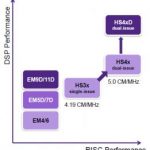

Is ARC HS4xD Family More a CPU or DSP IP Core?

When I had to define the various IP categories (processor, analog & mixed-signal, wired interfaces, etc.) to build the Design IP Report, I scratched my head for a while about the processor main category: how to define the sub-categories? Not that long ago, it was easy to identify a CPU IP core and a DSP IP core. As of today, if a DSP… Read More

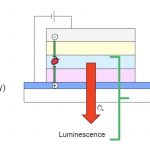

AIM Photonics Catching Its Stride as They Move into 2nd Year

AIM Photonics held its 2017 Proposers Meetings on May 24[SUP]th[/SUP] in Rochester, NY. The meetings included a review of AIM’s progress and strategic direction by their TRB (technical review board) and a session targeted at PIC (photonic integrated circuit) design for multi-project wafer (MPW) runs. While these discussions… Read More

TCAD for TFT, LCD and OLED Displays

As I write there are multiple displays in front of me that use TFT, LCD or OLED displays:

- ViewSonic Monitors with 24″ display

- MacBook Pro with 15″ display

- iPad Air

- Samsung Galaxy Note 4

- Nexus 7 tablet

- Garmin Edge 820

Getting to IP Functional Signoff

In the early days of IP reuse and platform-based design there was a widely-shared vision of in-house IP development teams churning out libraries of reusable IP, which could then be leveraged in many different SoC applications. This vision was enthusiastically pursued for a while; this is what drove reusability standards and … Read More

Embedded FPGA IP update — 2nd generation architecture, TSMC 16FFC, and a growing customer base

Regular Semiwiki readers are aware that embedded FPGA (eFPGA) IP development is a rapidly growing (and evolving) technical area. The applications for customizable and upgradeable logic in the field are many and diverse — as a result, improved performance, greater configurable logic capacity/density, and comprehensive… Read More

RTL Correct by Construction

Themes in EDA come in waves and a popular theme from time to time is RTL signoff. That’s a tricky concept; you can’t signoff RTL in the sense of never having to go back and change the RTL. But the intent is still valuable – to get the top-level or subsystem-level RTL as well tested as possible, together with collateral data (SDC, UPF, etc)… Read More

PDA will exhibit at the 54th DAC

Platform Design Automation, Inc will exhibit at the 54th Design Automation Conference(DAC) on June 18-21 in Austin Convention Center, Texas, USA, in Booth #1929. What to Expect:… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era