If you’re in the ASIC business, by now you should have a rough understanding of ISO 26262, the safety standard for automotive electronics. You may be less familiar with DO-254 which has somewhat similar intent for airborne electronics. Unless, that is, you design with FPGAs in which case your familiarity may be the other way around… Read More

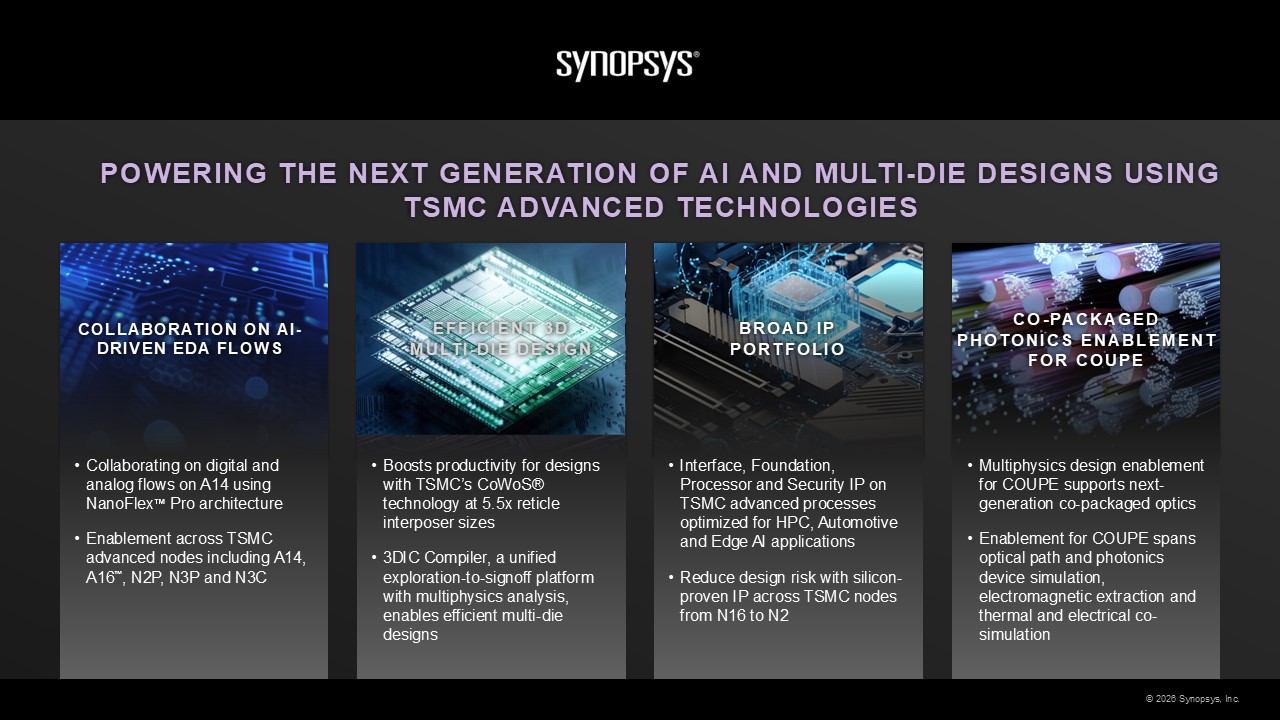

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

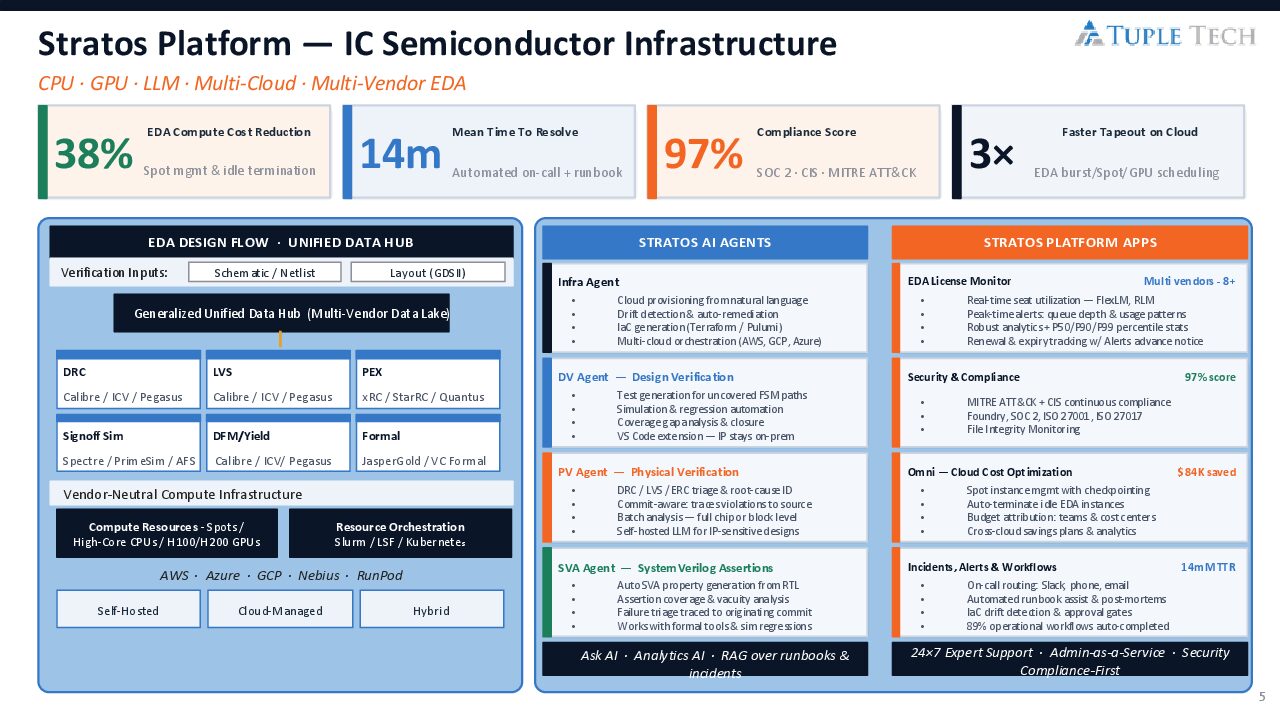

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreIoT Designs Beginning to Shift to 7nm: Promises Upside for Cadence Physically-Aware Design Flow

Until recently, ICs at bleeding edge nodes like 7nm technology from foundries like TSMC were mostly targeted for high-performance-computing (HPC) and mobile applications or possibly high radix switches that needed the increased performance of advanced nodes. The momentum of Moore’s law and Moore-than-Moore saw foundries… Read More

Global Semiconductor Market Trends ISS 2018

One of the other blog worthy analyst presentations at ISS 2018 was by Len Jelinek of IHS. Len is my kind of analyst, he spent 28 years in the semiconductor industry before going to the dark side so he knows what he is talking about. Len’s presentation on Global Semiconductor Market Trends is action packed so I will be doing a lot of cut … Read More

What GM Can Learn from Tesla

General Motors has had wireless connections to its cars for more than 21 years, thanks to Project Beacon, better known as OnStar, now operated as Global Connected Consumer Experience. OnStar has likely saved hundreds of lives, if not thousands, by summoning emergency responders to the scenes of crashes where airbags deployed.… Read More

Webinar: The Emergence of FPGA Prototyping for ASIC and SoC Design

One of the more interesting markets that I cover is FPGA Prototyping. Interesting because it is fast growing ($150-250M) and interesting because it is all about design starts and design starts are the lifeblood of the semiconductor industry.

If you are interested in FPGA prototyping you might want to start with the 30+ S2C Inc blogs… Read More

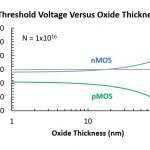

IEDM 2017 – Controlling Threshold Voltage with Work Function Metals

As I have said many times, IEDM is one of the premier conferences for semiconductor technology. On Sunday before the formal conference started I took the “Boosting Performance, Ensuring Reliability, Managing Variation in sub-5nm CMOS” short course. The second module in the course was “Multi-Vt Engineering… Read More

Wanted by January 30th: Paper for DAC IP Track 2018!

DAC 2018 will take place in San Francisco in June (24 to 28) and you have a fantastic opportunity to present a paper in the IP track! In fact, the deadline has been extended to January 30[SUP]th[/SUP] to submit your proposal.

Let’s make it clear: you are not expected to send the completed paper by this date, just the following:

- The title

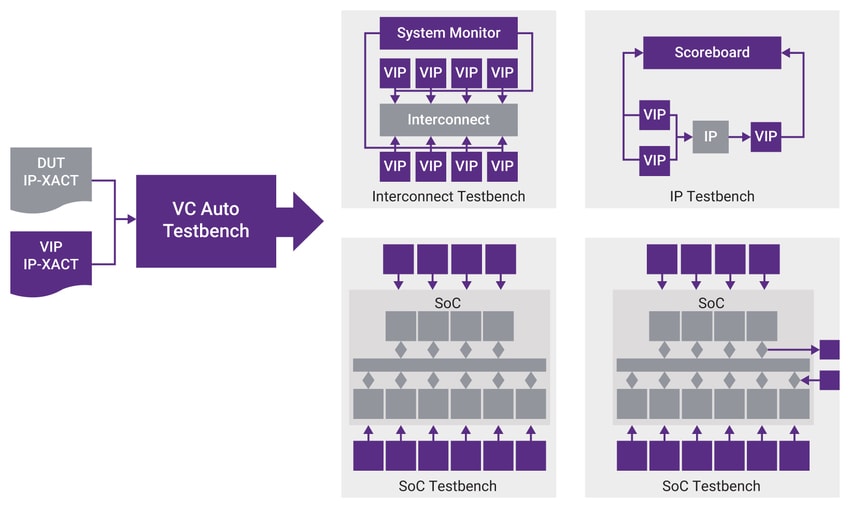

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

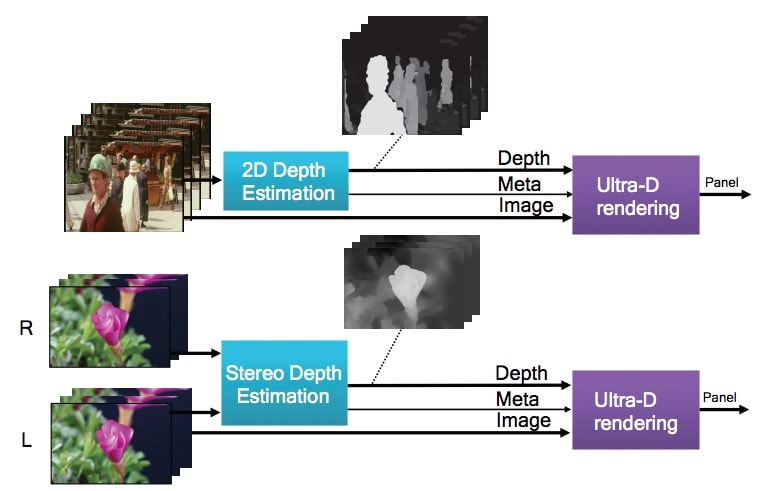

Designing an SoC for 3D TV Without using the Funny Glasses

In the blur of activities at DAC last year I visited the Mentor booth a few times and had just a few minutes to glance at a 3D TV display that didn’t require me to wear any funny glasses, kind of novel I thought at the time because I’ve read that the market of 3D TV sets is being hampered by requiring viewers to wear glasses. The… Read More

Context is Everything – especially for autonomous vehicle IP

GM has just announced that it will introduce a car with no steering wheel or pedals in 2019. According to their statement, they have already planned four phases of their autonomous driving system, and they will plan many more. However, before we jump into this latest car and not grab the wheel for a spin, it is reasonable to ask about… Read More

Siemens U2U 3D IC Design and Verification Panel