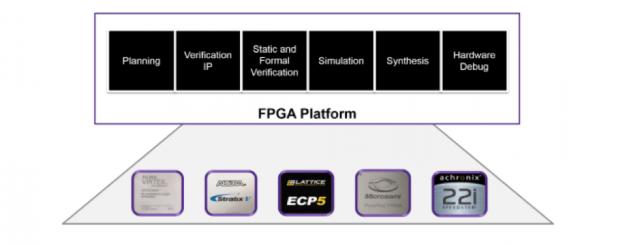

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

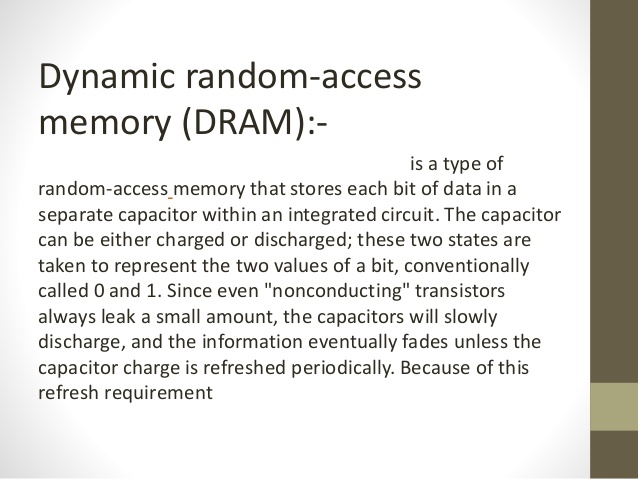

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreAre memory makers colluding against China?

Maybe OMEC is the new OPEC? A bargaining chip in June trade show down?

China has started an apparent investigation into pricing of DRAM memory with Samsung, Micron and SK Hynix as targets. We find this somewhat coincidental given the current trade issues. Memory pricing has been unusually strong for a very long time. Much longer … Read More

John Lee: Market Trends, Raising the Bar on Signoff

I talked to John Lee (GM of the ANSYS Semiconductor BU) recently about his views on market trends and the ANSYS big-picture theme for DAC 2018. He set the stage by saying he really liked Wally’s view on trends (see my blog on Wally’s keynote at U2U). John said these confirm what he is seeing – a trend to specialization, some around… Read More

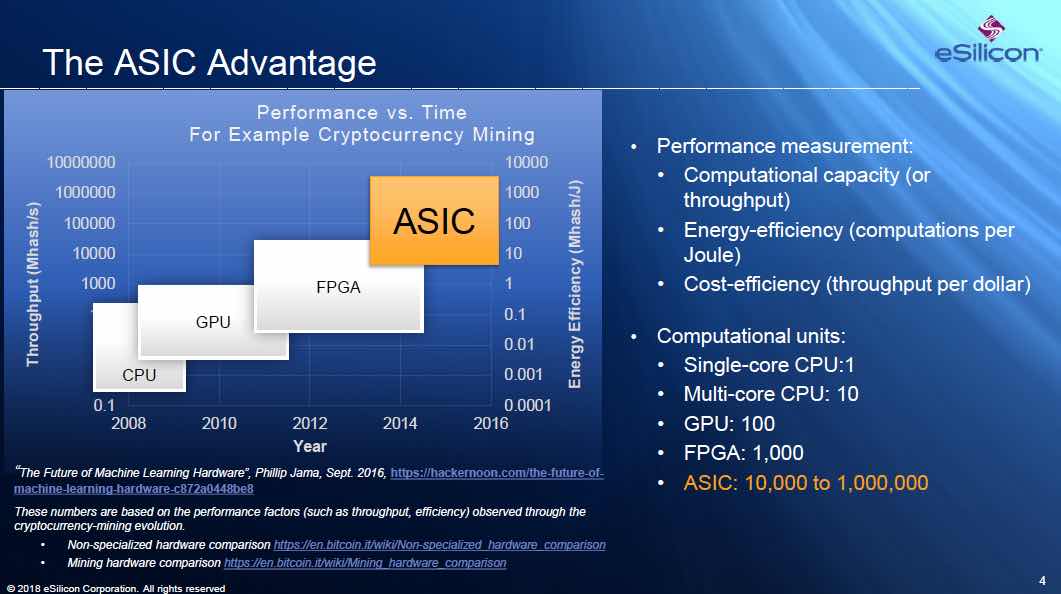

Being Intelligent about AI ASICs

The progression from CPU to GPU, FPGA and then ASIC affords an increase in throughput and performance, but comes at the price of decreasing flexibility and generality. Like most new areas of endeavor in computing, artificial intelligence (AI) began with implementations based on CPU’s and software. And, as have so many other applications,… Read More

SemiWiki and SmartDV on Verification IP

Bernard Murphy and I spent time with the SmartDV folks in preparation for the Design Automation Conference later this month. Bernard is an internationally recognized verification expert so his feedback is often sought after by emerging and leading verification companies, absolutely. Verification IP is a crowded market so … Read More

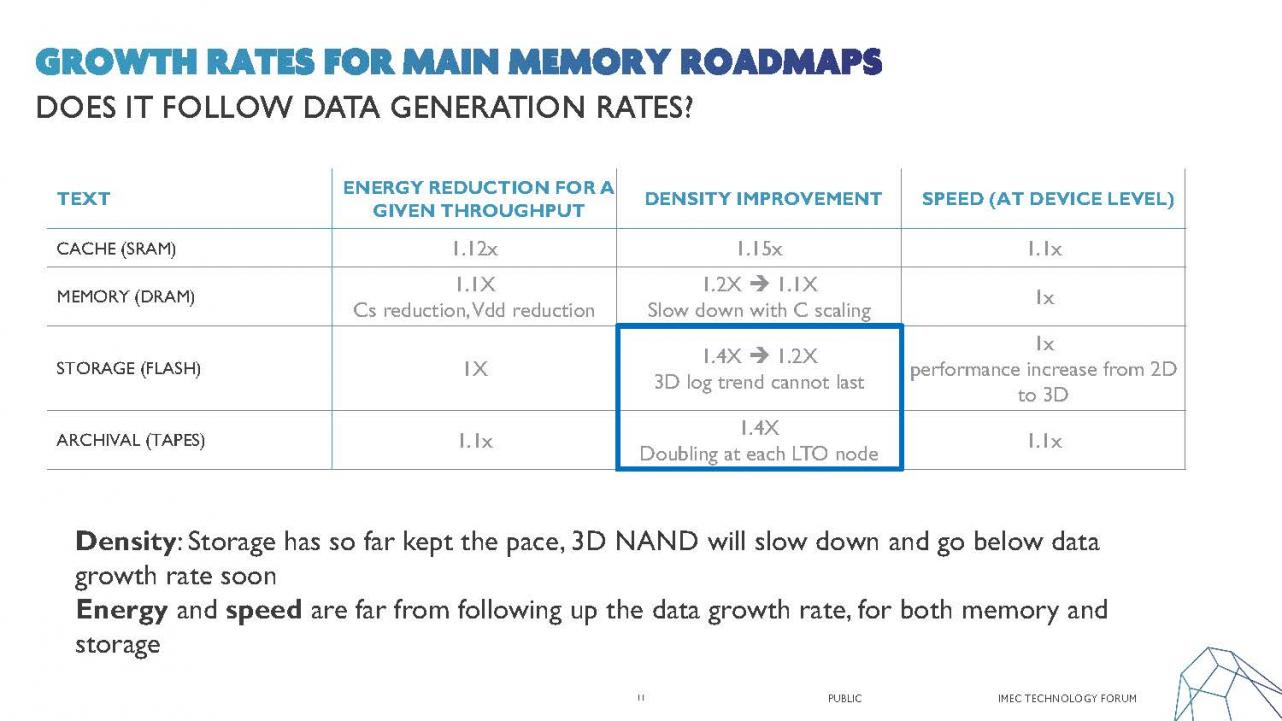

Imec technology forum 2018 – the future of memory

At the Imec technology forum in Belgium Gouri Sankar Kar and Arnaud Furnemont presented memory and storage perspectives and I also got to interview Arnaud. Arnaud leads overall memory development at Imec and personally leads NAND and DNA research.

Memory research is focused on power, energy, speed and cost with energy and throughput… Read More

Single-Chip Narrow-Band IoT

Many factors go into building a competitive solution for the IoT, but few are as important for high-volume applications as low cost – not just chip cost but total system cost. If your customers are going to deploy thousands, tens of thousands or even millions of your devices in cities, factories, logistics applications, power grids… Read More

Is there anything in VLSI layout other than “pushing polygons”? (10)

The year is 2005 and PMC Sierra decided that it is time to expand by adding a new site in Bangalore, India. We started with digital verification first but by 2006 we were ready to engage with Mixed Signal Design and Layout. I went to Bangalore in June 2006 for the first time and with the help of our local manager, Vikram Labhe, had a few layout… Read More

Mentor Siemens Update 2018

As you know I am a big fan of disruption and the Siemens acquisition of Mentor is turning out to be one of my favorite EDA disruptions. At first it was a little bit perplexing but after one short year it makes complete sense.

Siemens is acquiring Mentor as part of its Vision 2020 concept to be the Benchmark for the New Industrial Age. It’s… Read More

What Mary Meeker Missed

It must be a measure of the dim view taken of the automotive industry by Silicon Valley types that of the 294 slides in Mary Meeker’s annual Trends presentation delivered at this year’s Code Conference less than 10 of those slides refer to transportation. The Kleiner Perkins Caufield & Byers partner even managed to avoid… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!