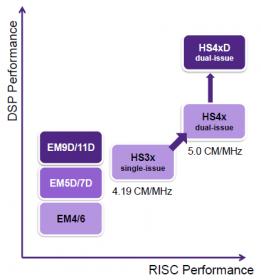

When I had to define the various IP categories (processor, analog & mixed-signal, wired interfaces, etc.) to build the Design IP Report, I scratched my head for a while about the processor main category: how to define the sub-categories? Not that long ago, it was easy to identify a CPU IP core and a DSP IP core. As of today, if a DSP is clearly dedicated to process digital signal, a CPU IP may also support these type of tasks, on top of the main processing/control function it was initially designed for. Synopsys DesignWare new ARC HS4xD family is a perfect example of a RISC CPU IP core offering 5.0 CoreMark/MHz (so we should rank it in the CPU IP category), being also capable of high performance pure DSP processing (but can we rank it into DSP IP category?).

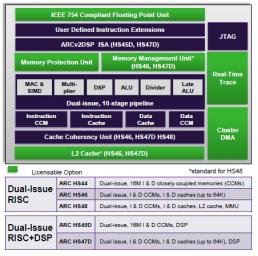

Let’s make it clear from the beginning: HS44, HS46, HS48 execute RISC only operations when HS45D and HS47D execute RISC and DSP (through ARCv2DSP). When combining RISC and DSP capabilities in a processor, the key is the software tools and library support, allowing seamless C/C++ programming and debug.

All the cores are supporting dual-issue, increasing utilization of functional units with limited amount of extra hardware. What is dual-issue? The capability for up to two instructions per clock, with in-order execution and the same software view as single issue. Dual-issue increases both RISC and DSP performance, but the area and power penalty is very decent, with only 15% increase. The instruction set has been improved to increase instruction per clock, allowing to execute multiple instructions in parallel and take benefit of the dual-issue pipeline.

While all the cores are supporting Instruction and Data Close Coupled Memory (CCM) from 512B to 16 MB, the designer will have to select HS46, HS47D or HS48 to benefit from Instruction and Data cache up to 64K, supporting cache coherency. The L2 cache (from 2MB to 8 MB) is available as an option for HS46 and HS47D, as well as MMU, but is by default supported by the HS48 core.

Such a core family can support a very wide range of applications, thanks to the high level of configurability. For example, all the cores support multi-core implementation, with single, dual or quad instances. Moreover, Synopsys proposes various licensable options, like FPU, MPU, MMU, real-time trace (RTT), L2 cache, FastMath Pack, cluster DMA or CoreSight Interface.

The HS4x RISC (only) family can address enterprise SSD processing needs, home networking, automotive control, wireless control or home automation.

With the HS4xD family, it’s possible to support mobile baseband, Voice/speech applications and multi-channel home audio or human machine interface.

HS4x(D) family has been tailored for embedded applications and any core is able to manage power budgets that are fixed, at best, or dropping. For any core, the power domain policy has been increased, offering user control over power management.

Every CPU IP vendor will claim offering the best solution, that’s why it could be wise to look at verified facts when comparing with the competition. Let’s talk about performance-efficiency rather than raw performance, as most of the applications need a tight control of power budget. Synopsys is claiming to offer best in class performance efficiency vs competition, with same or better features.

Some facts:

- 45% higher performance than Cortex-A9 at ½ the power consumption

- 2x higher performance than MIPS InterAptiv or Cortex-A7 at 20% lower power consumption

- 2.5 higher performance than Cadence Tensilica processors

- HS4x cores can be clocked at over 2.5 GHz in 16ff (typical), and this is faster than any core in this class

- HS48x2 delivers higher performance than Cortex-A17… at lower power than Cortex-A9

- HS family supports up to 8 contexts, when ARM and Cadence only support 1

So, “should we rank this DesignWare HS4xD IP core family in the CPU or DSP category?” is probably not the most crucial question, the real point to highlight is who (which competitor) and when this HS4xD family will be challenged by another IP vendor!

By Eric Esteve from IPnest

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.