Artificial Intelligence is one of the most talked about topics on the conference circuit this year and I don’t expect that to change anytime soon. AI is also one of the trending topics on SemiWiki with organic search bringing us a wealth of new viewers. You may also have noticed that AI is a hot topic for webinars like the one I am writing… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreTI Patent Priorities

This is the seventh in the series of “20 Questions with Wally Rhines”

Probably the most innovative person I met at Texas Instruments, other than Jack Kilby, was Ken Bean. Ken had a list of patents that would impress even the most skeptical. He started his career at Eagle Picher and came to TI in the mid 1960s. He was a warm,… Read More

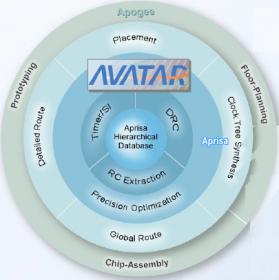

Aprisa and Apogee – The New Avatars

Earlier physical optimization impacts a design QoR gain and can disclose potential hurdles in dealing with unknown design variants such as new IP inclusion or new process node issues. Along the RTL-to-GDS2 implementation continuum, a left-shift move requires a robust modeling and proper context captures in order to produce… Read More

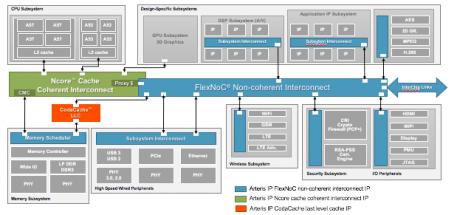

A Last-Level Cache for SoCs

We tend to think of cache primarily as an adjunct to processors to improve performance. Reading and writing main memory (DRAM) is very slow thanks to all the package and board impedance between chips. If you can fetch blocks of contiguous memory from the DRAM to a local on-chip memory, locality of reference in most code ensures much… Read More

Machine Learning and Embedded FPGA IP

Machine learning-based applications have become prevalent across consumer, medical, and automotive markets. Still, the underlying architecture(s) and implementations are evolving rapidly, to best fit the throughput, latency, and power efficiency requirements of an ever increasing application space. Although ML is … Read More

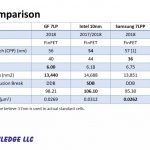

SEMICON West Intel 10nm and GF 7nm Update

SEMICON West seemed a little slow last week but maybe it was just me. I’m sure SEMI will come out with record breaking numbers but I did not see it in the exhibit hall (see the video). What I did see was hundreds of exhibitors but I had no idea what they did. San Francisco again was very congested and smelly. I talked to a friend who is in public… Read More

Accelerated Verification with Synopsys

At DAC 2018, Synopsys held a lunch panel discussing verification challenges faced by the industry leaders, their adopted approaches and the overall verification technology trends. This panel of industry experts from Intel, AMD, Samsung, STM and Qualcomm also shared their viewpoints on what drives the SoC complexity and how… Read More

Platform ASICs Target Datacenters, AI

There is a well-known progression in the efficiency of different platforms for certain targeted applications such as AI, as measured by performance and performance/Watt. The progression is determined by how much of the application can be run with specialized hardware-assist rather than software, since hardware can be faster… Read More

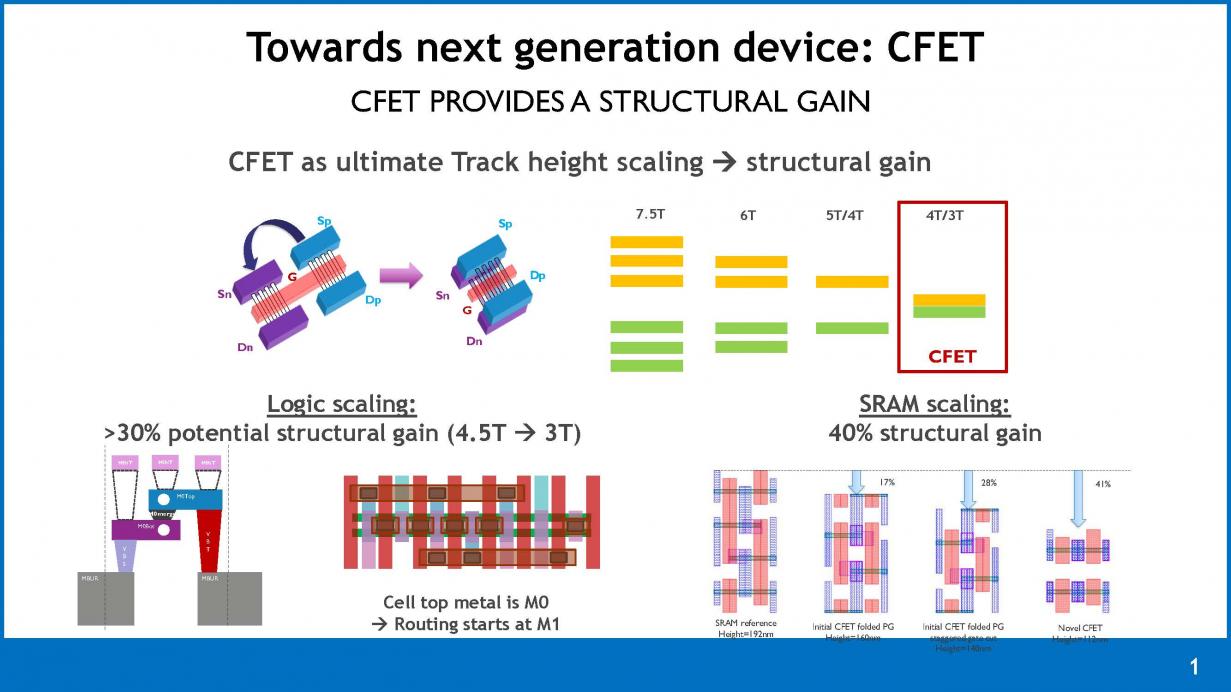

VLSIT Conference – imec on CFETs

The 2018 VLSI Technology conference was held in Hawaii in June and is one of the premier conferences covering integrated circuit process technology and circuit design. The Complementary FET (CFET) is an emerging option to continue logic scaling into the next decade. At the conference imec, GLOBALFOUNDRIES, Tokyo Electron and… Read More

Semicon Wrap Up holding pattern in turbulent air

The stock market hates uncertainty most of all. In the absence of the known, the market will assume the worst or close to it. Right now there is a lot of uncertainty that continues to have more downside beta than upside beta. Everybody we spoke to at Semicon wakes up in the morning wondering what tweet was sent at 5AM that will impact their… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!