The automotive industry is a world of contradictions. Nowhere is this more evident than in the realm of connected cars. Car makers remain utterly conflicted over connecting cars 21 years after General Motors got the ball rolling with the introduction of OnStar.

Even GM had to famously be goaded into connecting its cars by then executive… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

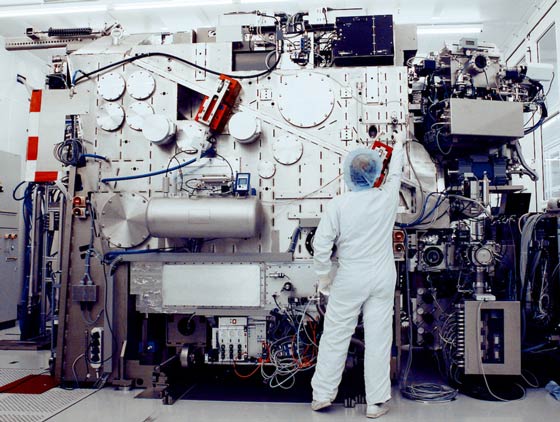

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreLithoVision 2019 – Semiconductor Technology Trends and their impact on Lithography

I was asked to present at Nikon’s LithoVision event again this year. LithoVision is held the day before the SPIE Advanced Lithography Conference also in San Jose. The following is a write up of my talk.… Read More

Report from SPIE EUV Update 2019

Not as much new – No breakthrough announcements, 300 watts is better than 250 watts – Pellicle Problems, TSMC is EUV king – Third times a charm? We attended this years SPIE Lithography convention in San Jose as we have for many years. Although the show was quite enthusiastic and EUV was the central topic, as it has… Read More

Synopsys GLOBALFOUNDRIES and Automotive IP

IP vendors have always had the inside track on the status of new process nodes and what customers are planning for their next designs. This is even more apparent now that systems companies are successfully doing their own chips by leveraging the massive amounts of commercial IP available today. Proving once again that IP really … Read More

Can I Trust my Hardware Root of Trust?

Hardware Roots of Trust (HRoTs) have become a popular mechanism to provide a foundational level of security in a cell-phone or IoT device or indeed any device that might appear to a hacker to be a juicy target. The concept is simple. In order to offer credible levels of security, any level in the stack has to be able to trust that levels… Read More

How Well Did Methodics do in 2018?

In January I read from the ESDA Allianceabout EDA and Semiconductor IP revenues increasing 6.7% for Q3 2018, reaching $2,435.6 million, which is decent growth for our maturing industry. In stark contrast there’s a company called Methodicsthat specializes in Intellectual Property Lifecycle Management (IPLM) and traceability… Read More

Safety: Big Opportunity, A Long and Hard Road

Safety, especially in road vehicles (cars, trucks, motorcycles, etc.), gets a lot of press these days. From the point of view of vendors near the bottom of the value chain it can seem that this just adds another item to the list of product requirements; as long as you have that covered, everything else remains pretty much the same in… Read More

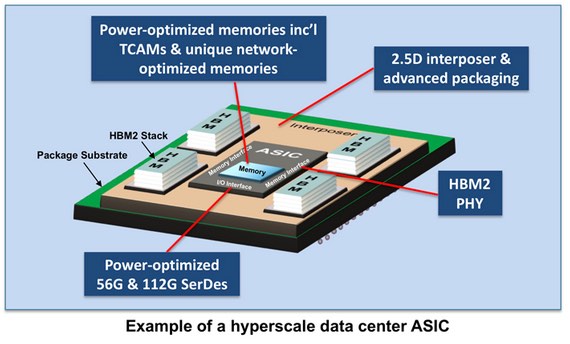

eSilicon Expands Expertise in 7nm

At SemiWiki we usually don’t write about the press releases we are sent. However, a recent press release by eSilicon caught my eye and prompted me to call Mike Gianfagna, eSilicon Vice President of Marketing. The press release is not just about one thing, rather it focuses on a number of interesting things that together show their… Read More

Interview with Bob Smith, Executive Director of the ESD Alliance

Bob Smith is executive director of the ESD (for electronic system design) Alliance that many Semiwiki readers will remember as the EDA Consortium. As Bob explains, the semiconductor industry is changing and evolving, and the electronic system design ecosystem with it. I encourage you to take a break from what you’re doing and … Read More

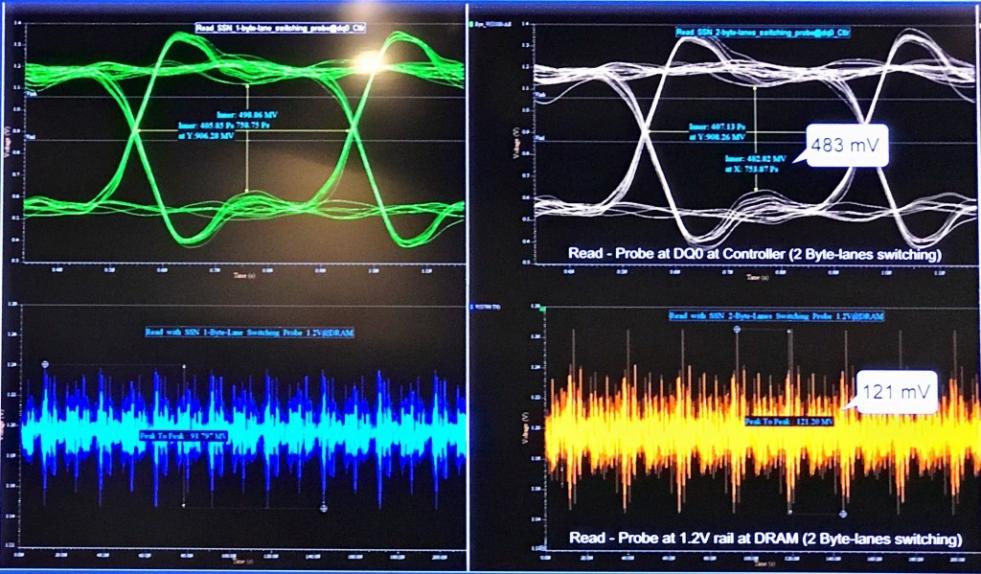

Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center