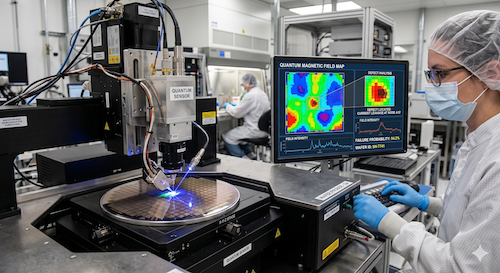

There were quite a few announcements at the Silicon Catalyst event at the Computer History Museum last week. The event itself was eventful with semiconductor legends in the audience and on the stage. First let’s talk about the announcements Silicon Catalyst made then we will talk about the event itself.

In addition to expanding… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior