Many times i notice people “kind of afraid” of some protocol, trying to avoid the usage because “it’s complicated”, I decide to go in-depth in one and show that maybe it’s not so complicated after all. First challenge is choosing the protocol and decide about the Ethernet, because this protocol… Read More

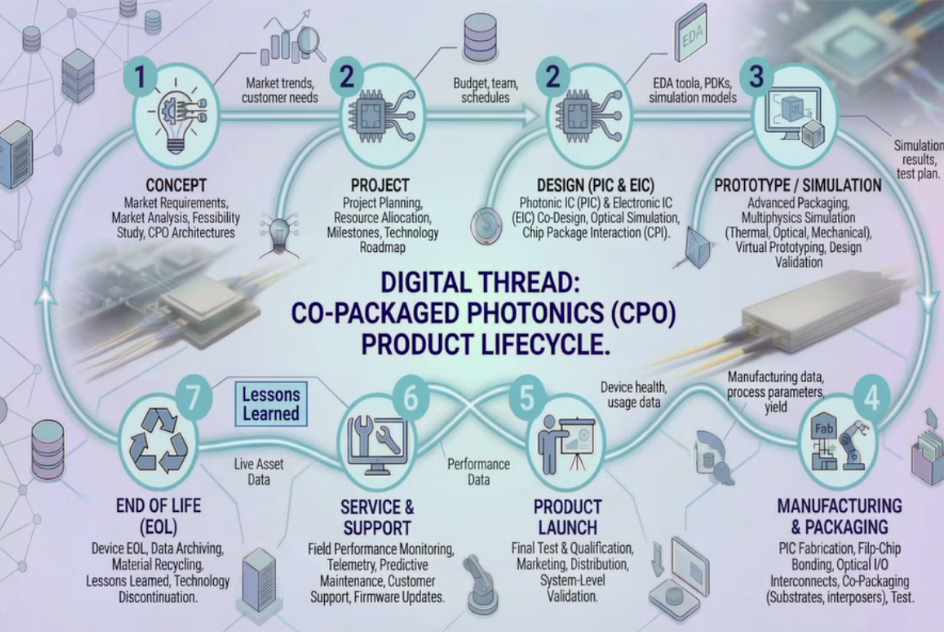

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More

RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read MoreWEBINAR: Design Adaptive eFPGA IP

Since the start of PROMS, PLDs and FPGAs we have learned the importance of programmability in modern semiconductor design. Today we have eFPGAs for “design adaptive” embedded programmability and that is what this webinar is all about.

Several key points are discussed starting with the Law of Accelerating Returns as it applies… Read More

The History and Physics of Cliosoft’s Academic Program!

It was a very late evening, perhaps 11 PM, on a warm summer night in 2008. Someone sent an email to info@cliosoft.com with a very odd question – why were we not listed in Wikipedia? The sender was a scientist working for the Lawrence Berkeley National Lab. Of course, this piqued my curiosity and I replied back asking why that concerns… Read More

Parallel-Based PHY IP for Die-to-Die Connectivity

Synopsys has released a Technical Bulletin entitled “Parallel-Based PHY IP for Die-to-Die Connectivity”. The piece is authored by Manuel Mota, senior product marketing manager, staff at Synopsys. Manuel has worked at Synopsys for 11 years in the IP area. Prior to that, he worked at MIPS Technologies, Chipidea (acquired… Read More

Anirudh CadenceLIVE Plays Up Computational Software

Cadence has clearly found its groove with Intelligent System Design, something that Lip-Bu reinforced in the CadenceLIVE kickoff keynote on Tuesday, August 11th. Anirudh Devgan, president of Cadence, continued to discuss the theme in his keynote on Wednesday, August 12th with his equally consistent subtitle—”Strength… Read More

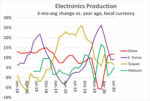

Electronics Production Healthy

Global electronics production is healthy, despite the COVID-19 pandemic. The chart below shows the three-month-average change versus a year ago (3/12 change) in electronics production (measured in local currency) for the major Asian producers. China is the largest electronics manufacturing country and the original source… Read More

Reverse-engineering the First FPGA Chip Xilinx XC2064

A Field-Programmable Gate Array (FPGA) can implement arbitrary digital logic, anything from a microprocessor to a video generator or crypto miner. An FPGA consists of many logic blocks, each typically consisting of a flip flop and a logic function, along with a routing network that connects the logic blocks. What makes an FPGA… Read More

GLOBALFOUNDRIES Goes Virtual with 2020 Global Technology Conference Series!

GlobalFoundries is one of the more interesting semiconductor stories of this decade. They started as a spinout of the AMD fabs then acquired Chartered Semiconductor Manufacturing in 2009 and the IBM Microelectronics business in 2014.

Now that events are virtual it is a great time for my fellow semiconductor professionals to

AI in Korea. Low-Key PR, Active Development

Based on press coverage and technical paper volume, you could be forgiven for thinking that Korea had decided to take a pass on AI mania, or maybe just to dabble a little here and there to stay abreast of trends. But you’d be wrong. Korea is very active in AI; they don’t feel a need to trumpet what they’re doing from the rooftops. If you … Read More

Trusted IoT Ecosystem for Security – Created by the GSA and Chaired by Mentor/Siemens

There’s a lot to keep you awake at night these days. If you live in California, it’s wildfires and unbreathable air. If you live on planet Earth, it’s COVID-19. And if you’re part of the value chain for IoT, it’s the security and robustness of the silicon and software fabric that connects our world. This fabric connects everything,… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea