Equalizers were initially designed and developed for movie theaters and amphitheaters or outdoor areas but now they have become ubiquitous. Equalization is essential for creating professional sound and creating real life like sound effects. Equalizers are used for controlling the energy/loudness of a particular frequency… Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

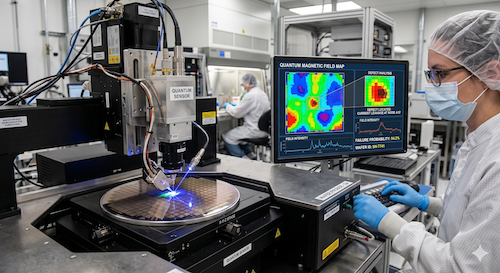

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read MorePodcast EP10: The M&A Landscape for Semis and EDA

Dan and Mike are once again joined by Dr. Walden Rhines for an overview of the M&A scene for semiconductors and EDA. Wally discusses the periodic expansion and contraction of these markets along with the factors that cause these trends. Wally concludes with a view of the future.

Wally Rhines is widely recognized as an expert … Read More

Webinar: Samtec Teams with Otava and Avnet to Tame mmWave Design

mmWave design has traditionally been a boutique technology used in satellite and defense applications. Lately that’s changing. It turns out the complex, high frequency capabilities of mmWave technology are a key enabler for the 5G wireless networks being deployed today. I discussed some of this backstory in a recent post about… Read More

CEO Interview: Dr. Shafy Eltoukhy of OpenFive

Dr. Shafy Eltoukhy has over 35 years of experience in the semiconductor industry. He served as VP and BU manager of the Analog Mixed Signal Group at Microsemi. He was the VP of Operations and Technology Development at Open-Silicon. He was the VP of Technology at Lightspeed Semiconductor where he joined the founding team that invented… Read More

Perforce Embedded DevOps Summit 2021 and the Path to Secure Collaboration on the Cloud

Perforce recently held their virtual Embedded DevOps Summit. There was a lot of great presentations across many disciplines. Of particular interest to me, and likely to the SemiWiki readership as well, was a presentation by Warren Savage entitled Secure Collaboration on a Cloud-based Chip Design Environment. I’ll provide … Read More

Maximizing ASIC Performance through Post-GDSII Backend Services

ASICs by definition are designed to meet the respective applications’ requirements. ASIC engineers deploy various design techniques to maximize performance, minimize power and reduce chip size. But is there more that can be done after the GDSII is taped out? A recent press release from Alchip Technology dated Feb 4, 2021 claims… Read More

NetApp Enables Secure B2B Data Sharing for the Semiconductor Industry

Data sharing between semiconductor companies and EDA software companies has been critical to the advancement of the industry. But it’s had security issues and associated loss of trust along the way. For instance, there have been cases of customer designs shared as a testcase finding their way into a product demo without the … Read More

Semiconductor Shortage – No Quick Fix – Years of neglect & financial hills to climb

– Semi Situation Stems from long term systemic neglect

– Will require much more than money & time than thought

– Fundamental change is needed to offset the financial bias

– Auto industry is just the hint of a much larger problem

Like recognizing global warming when the water is up to your neck

The problem… Read More

TECHTALK: Hierarchical PI Analysis of Large Designs with Voltus Solution

Power integrity analysis in large chip designs is especially challenging thanks to the huge dynamic range the analysis must span. At one end, EM estimation and IR drop through interconnect and advanced transistor structures require circuit-level insight—very fine-grained insight but across a huge design. At the other, activity… Read More

USB4 Makes Interfacing Easy, But is Hard to Implement

USB made its big splash by unifying numerous connections into a single cable and interface. At the time there were keyboard ports, mouse ports, printer ports and many others. Over the years USB has delivered improved performance and greater functionality. However, as serial interfaces became more popular and started being used… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior