Siemens EDA’s Veloce emulation products are long-established and worthy contenders in any emulation smack-down. But there was always a hole in the complete acceleration story. Where was the FPGA prototyper? Current practice requires emulation for fast simulation with hardware debug, plus prototyping for faster simulation… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreCertitude: Tool that can help to catch DV Environment Gaps

Design verification (DV) is still one of the biggest challenges in the ASIC based product world. In last two decades, we have seen many changes in terms of HVLs and methodologies used for design verification. System Verilog is the most popular HVL these days and UVM is the most popular verification methodology.

Even after such an… Read More

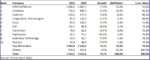

The Juggernaut Continues as ESD Alliance Reports Record Revenue Growth for Q4 2020

Apologies for the slightly hyperbolic title of this post. Webster defines Juggernaut as “a massive inexorable force, campaign, movement, or object that crushes whatever is in its path.” Marvel Comic fans will recall the term also refers to a superhero nemesis. But I digress. The ESD Alliance recently announced its Q4 2020 Electronic… Read More

Design IP Sales Grew 16.7% in 2020, Best Growth Rate Ever!

Design IP Sales Grew 16.7% in 2020, to reach $4.6B and this is the best growth since year 2000!

The main trends shaking the Design IP in 2020 are very positive for the Top 3 IP vendors, each of them growing more than the market and confirm the importance of the wired interface IP market, aligned with the data-centric application, hyperscalar,… Read More

How PCI Express 6.0 Can Enhance Bandwidth-Hungry High-Performance Computing SoCs

What do genome sequencing, engineering modeling and simulation, and big data analytics have in common? They’re all bandwidth-hungry applications with complex data workloads. High-performance computing (HPC) systems deliver the parallel processing capabilities to generate detailed and valuable insights from these applications.

eFPGA IP – in Videos

eFPGA has been a hot topic on SemiWiki for the past five years and it is still going strong. eFPGA is more descriptively categorized as embedded programmable logic and reconfigurable computing. Whatever you want to call it, eFPGA is an important piece of the computing puzzle, absolutely.

We recently did a series of videos with Menta… Read More

Meeting the Need for Hardware-Assisted Verification

Editor’s Note: Siemens EDA recently introduced a comprehensive hardware-assisted verification system comprised of hardware, software and system verification that streamlines and optimizes verification cycles while helping reduce verification cost. What follows is an edited version of an interview Verification Expert… Read More

Apple’s Cook Paints Himself into an Autonomous Corner

These days tech journalists and analysts appear confident of one thing. Apple is working on an autonomous car.

There’s a “Garbo Talks” quality to the tea leaf reading around Apple’s autonomous vehicle development efforts. The latest chapter was written with the publication of Kara Swisher’s latest “Sway” podcast episode

Technology Under Your Skin: 3 Challenges of Microchip Implants

As technology continues to get closer to merge with our bodies, from the smart phones in our hands to the smartwatches on our wrists to earbuds. Now, it’s getting under our skin literally with a tiny microchip. A human microchip implant is typically an identifying integrated circuit device or RFID (Radio-Frequency IDentification)… Read More

Podcast EP15: The Birth of Dynamically Reconfigurable Computing

Dan and Mike are joined by Geoff Tate, founding CEO of Flex Logix. Geoff has a storied career in semiconductors that includes over ten years at AMD, ending as senior VP, microprocessors and logic. Following AMD, Geoff was founding CEO of Rambus, growing the company from four people to IPO with a $2 billion market cap.

As co-founder… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center