For those not familiar with Fierce Technology, this firm offers a one stop place for news, analysis and education in the areas of telecom, wireless, sensors and all related electronics markets. They organize popular events such as the 5G Blitz Week, Sensors Innovation Week series, Sensors Converge and many more. These events … Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreWEBINAR: How to Improve IP Quality for Compliance

Establishing traceability is critical for many organizations — and a must for those who need to prove compliance. Too often, the compliance process is manual, leading to errors and even delays. A simple clerical mistake can invalidate results and lead to larger issues throughout the product’s lifecycle. Developing a unified,… Read More

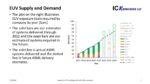

Intel and the EUV Shortage

In my “The EUV Divide and Intel Foundry Services” article available here, I discussed the looming EUV shortage. Two days ago, Intel announced their first EUV tool installed at their new Fab 34 in Ireland is a tool they moved from Oregon. This is another indication of the scarcity of EUV tools.

I have been tracking EUV system production… Read More

Python in Verification. Veriest MeetUp

Veriest held a recent meetup on a topic that has always made me curious – use of Python in verification. The event, moderated by Dusica Glisic (technical marketing manager at Veriest), started with an intro from Moshe Zalcberg (CEO of Veriest) and talks by Avidan Efody (Apple verification) and Tamás Kállay (Team leader, Veriest).… Read More

Benefits of a 2D Network On Chip for FPGAs

The reason people love FPGAs for networking and communications applications is because they offer state of the art high speed interfaces and impressive parallel processing power. The problem is that typically a lot of the FPGA fabric resources are used simply to move the data on or off and across the chip. Achronix has cleverly … Read More

Spatial Audio: Overcoming Its Unique Challenges to Provide A Complete Solution

“If a tree falls in a forest and no one is around to hear it, does it make a sound?” is a philosophical thought experiment that raises questions regarding observation and perception [Source: Wikipedia]. Setting aside the philosophical aspects, if one wasn’t present where a sound was generated, the sound was lost forever.… Read More

ISO 26262: Feeling Safe in Your Self-Driving Car

The word “safety” can mean a lot of different things to different people, but it’s a word we hear frequently when the topic involves automobiles. In contrast, “functional safety” has a long-established meaning in the design of electrical and mechanical systems: an automatic protection mechanism with a predictable response … Read More

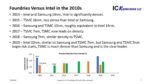

Can Intel Catch TSMC in 2025?

At the ISS conference held from April 4th through 6th I presented on who I thought would have the leading logic technology in 2025. The following is a write up of that presentation.

ISS was a virtual conference in 2021 and I presented on who currently had logic leadership and declared TSMC the clear leader. Following that conference,… Read More

The ESD Alliance CEO Outlook is Coming April 28 –– Live!

It’s not often our community is able to attend an in-person discussion where executives share their insights on industry trends, especially over the past two years as the pandemic swept across the globe.

Well, that’s about to change and I suggest you start jotting down questions as the ESD Alliance plans its first in-person CEO … Read More

Chip Shortage Killed the Radio in the Car

“In my mind and in my car, we can’t rewind we’ve gone too far.” – “Video Killed the Radio Star” – The Buggles

I discovered within days of driving home my new BMW X3 last fall that I was a victim of the much ballyhooed chip shortage. Among the features “deleted” from … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center