“Inverse lithography technology (ILT) represents the most significant EDA advance in the last two decades.” Danping Peng from TSMC made that assertion at the recent SPIE Advanced Lithography + Patterning Conference, in his talk entitled: ILT for HVM: History, Present, and Future. This article summarizes the highlights… Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read MoreUnlock first-time-right complex photonic integrated circuits

The capacity and energy efficiency challenges from the growing appetite for high-speed data along with advanced applications such as LIDAR and quantum computing are driving demand for increasingly large-scale photonic integrated circuits (PIC). With an ever-increasing number of components on a single photonic chip, manual… Read More

Coding Guidelines for Datapath Verification

It has been an article of faith that you can’t use formal tools to validate datapath logic (math components). Formal is for control logic, not datapath, we now realize. We understood the reason – wide inputs (32-bit, 64-bit or more) fed through a multiplier deliver eye-watering state space sizes. State space explosions also happen… Read More

Importance of an Analytics Platform Before Migrating to the Cloud

After many years of hesitancy to jump with both feet in, semiconductor companies are seriously considering implementing cloud strategies and making required investments. Their concern though is, how much investment is it going to take? Some of the block-and-tackle challenges they face in implementing a cloud strategy are … Read More

0.55 High-NA Lithography Update

At the recent SPIE Advanced Lithography + Patterning Conference, Mark Phillips from Intel gave an insightful update on the status of the introduction of the 0.55 high numerical aperture extreme ultraviolet lithography technology. Mark went so far as to assert that the development progress toward high-NA EUV would support … Read More

Using EM/IR Analysis for Efinix FPGAs

I’ve been following the EM/IR (Electro-Migration, IR is current and resistance) analysis market for many years now, and recently attended a presentation from Steven Chin, Sr. Director IC Engineering of Efinix, at the User2User event organized by Siemens EDA. The Tuesday presentation was in the morning at the Marriott… Read More

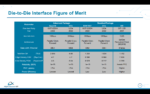

Die-to-Die IP enabling the path to the future of Chiplets Ecosystem

The topic of chiplets is getting a lot of attention these days. The chiplet movement has picked up more momentum since Moore’s law started slowing down as process technology approached 5nm. With the development cost of a monolithic SoC crossing the $500M and wafer yields of large die-based chips dropping steeply, the decision … Read More

Connecting Everything, Everywhere, All at Once

The automotive industry is rapidly coming to the realization that connecting cars is about so much more than simply adding a modem, an antenna, and a bit of software. Connecting cars and connecting car owners with an attractive connectivity value proposition may be two of the most difficult things the industry has ever attempted.… Read More

Podcast EP82: The Critical Need for Reliability in Future Products

Dan is joined by Charlie Slayman, technical leader at Cisco Systems working on reliability physics and risk assessment of advanced semiconductor technology. He is also the general chair of the International Reliability Physics Symposium, or IRPS which is the focus of the discussion.

Dan explores the rapidly growing application… Read More

The New Normal for Semiconductor Manufacturing

One of the recent live events I attended was the 2022 GSA Silicon Leadership Summit on May 12th at the Santa Clara Convention Center (my favorite location). This was the first GSA live event in two years so it was a must attend gathering. This event targets semiconductor ecosystem executives (200+ people attended) so there were many… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era