Very recently, 3GPP announced that 5G Release 17 was finalized. One important consequence is that 5G RedCap (reduced capacity) is now real and that means 5G becomes accessible to IoT devices. Think smart wearables (e.g. watches), industrial sensors and surveillance devices. “So what?”, you protest. “I don’t need 5G on my watch.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read MoreUsing AI in EDA for Multidisciplinary Design Analysis and Optimization

Most IC and system engineers follow a familiar process when designing a new product: create a model, use parameters for the model, simulate the model, observe the results, compare results versus requirements, change the parameters or model and repeat until satisfied or it’s time to tape out. On the EDA side, most tools perform… Read More

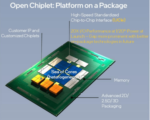

Verifying Inter-Chiplet Communication

Chiplets are hot now as a way to extend Moore’s Law, dividing functionality across multiple die within a single package. It’s no longer practical to jam all functionality onto a single die in the very latest processes, exceeding reticle limits in some cases and in others straining cost/yield. This is not an academic concern. Already… Read More

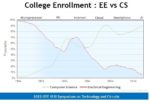

A Crisis in Engineering Education – Where are the Microelectronics Engineers?

At the recent VLSI Symposium on Technology and Circuits, a panel discussion presented a jarring forecast. The theme of the panel was “Building the 2030 Workforce: How to Attract Great Students and What to Teach Them?”, with participants from academia and industry, as well as a packed (and vocal) audience.

On the one hand, the … Read More

Supply Chain Verification: Critical Enabler for Next-Generation Medtech Innovations

Chip design verification has long been a key component of any design project developing silicon intended to go into manufacturing. As designs become more complex, so does the manufacturing risk, and the focus on thorough verification becomes ever more critical.

Another dimension of complexity coming into play and considered… Read More

Micron kicks off the down cycle – Chops 2023 capex – Holding inventory off street

-Micron reports weak outlook for fiscal Q4

-2023 capex to be down versus 2022 capex of $12B & Q3’s $2B

-Company keeping inventory off street to support pricing

-Memory is usually the first shoe to drop in a down cycle

Sharp drop in demand at end of Q3…..

Micron reported a sharp drop in demand at the end of its fiscal Q3,… Read More

Semiconductor Hard or Soft Landing? CHIPS Act?

-Chip cycle will come down. Only question is landing impact

-What does cyclical end do to re-shoring & build out plans?

-Is it less demand, excess supply or both? Does it matter?

-CHIP Act rescue efforts get desperate switching to threats

Any landing you can walk away from is a good one

For those of us who have been in the semiconductor… Read More

Podcast EP92: The Impact of a Specification-Driven Correct-by-Construction Approach on Design and Verification with Agnisys

Dan is joined by Anupam Bakshi, founder and CEO of Agnisys. Anupam has more than two decades of experience implementing a wide range of products and services in the high tech industry. Prior to forming Agnisys, he held various management and technical lead roles at companies such as Avid Technology Inc., PictureTel, Blackstone,… Read More

The Lines Are Blurring Between System and Silicon. You’re Not Ready.

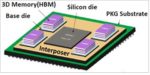

3D-ICs bring together multiple silicon dies into a single package that’s significantly larger and complex than traditional systems on a chip (SoCs). There’s no doubt these innovative designs are revolutionizing the semiconductor industry.

3D-ICs offer a variety of performance advantages over traditional SoCs. Because … Read More

Cadence Execs Look to the Future

Everything is becoming digital, and everything digital requires semiconductors. Cadence’s President and CEO, Dr. Anirudh Devgan, highlighted this at the recent CadenceLIVE user conference and discussed many of the company’s accomplishments and future directions. Dr. Devgan also sees the emergence of data—especially … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center