Dan is joined by Marc Hutner. Marc has been innovating in the areas of design, test, DFT and data analytics for more than 20 years. In June of 2023, he joined the Siemens EDA Tessent group as the product director of Silicon Learning, enabling how silicon data is applied to yield improvement and silicon debug. Previously, he worked … Read More

At the VLSI Technology Symposium this week Intel released details on their i3 process. Over the last four nodes Intel has had an interesting process progression. In 2019, 10nm finally entered production with both high performance and high-density standard cells. 10nm went through several iterations eventually resulting in… Read More

The week before DAC I had the privilege to take a video call with Pradeep Thiagarajan – Product Manager, Simulation, Custom IC Verification at Siemens EDA to get an update on new simulation products. I’ve been following Solido for years now and knew that they were an early adopter of ML for Monte Carlo simulations with SPICE users.… Read More

Dan is joined by Sathishkumar Balasubramanian. Sathish currently leads the product management and marketing organization for CustomIC Verification (CICV) division at Siemens. Sathish is an experienced product leader with over 20+ years of experience in the EDA industry.

Sathish’s focus is on bringing value to the semiconductor… Read More

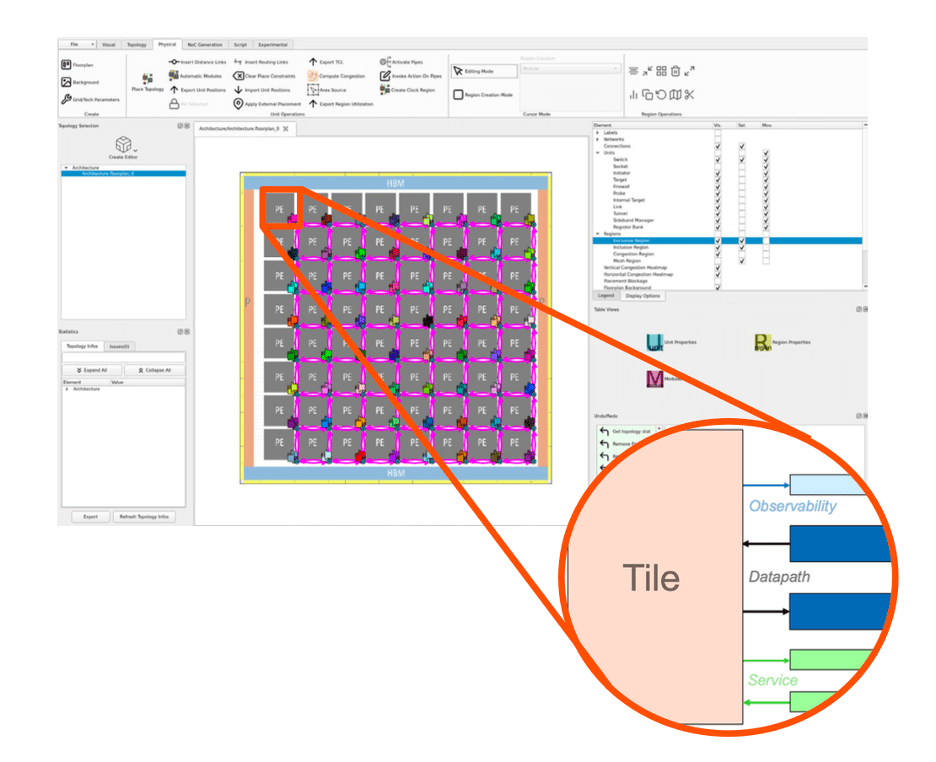

Heterogeneous multi-die integration is gaining more momentum all the time. The limited roadmap offered by Moore’s Law monolithic, single-die integration has opened the door to a new era of more-than-Moore heterogeneous integration. The prospects offered by this new design paradigm are exciting and the entire ecosystem is… Read More

An emerging trend with IC design is the growing use of chiplets and even 3D IC designs, as the disaggregated approach has some economic and performance benefits over a single SoC. There are thermal challenges with using chiplets and 3D IC designs, so that means that thermal analysis has become more important. I just spoke with Michael… Read More

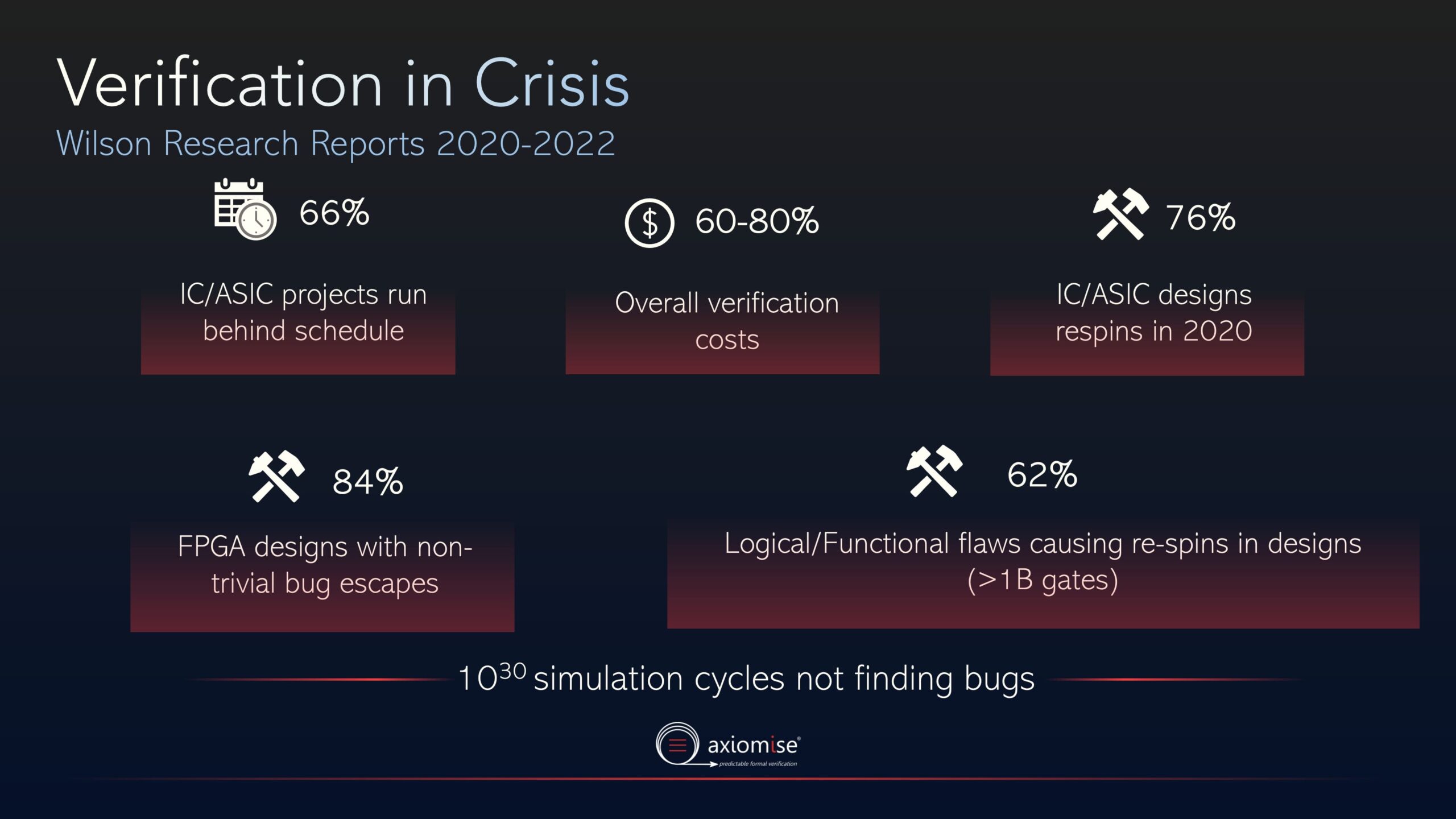

Coverage improvement effectiveness through randomized testing declines as total coverage improves. Attacking stubborn holes in coverage could be augmented through learned novel test guidance to random test selection. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former… Read More

Systems engineers often want to select the best IC for their projects, yet the time required to search online, buy an Evaluation Kit, waiting to receive it in the mail, then getting it installed and setup for testing can be a barrier and lengthen the project timeline. This is where TenXer Labs comes in, as they have cleverly developed… Read More

Dan is joined by Dr. John Ferguson, senior director of marketing for the Calibre product line at Siemens EDA. John has worked extensively in physical design verification. Current activities include efforts to extend physical verification and PDK enablement for 3DIC design and silicon photonics.

Dan explores the Siemens EDA… Read More

In the rapidly evolving world of high-performance computing (HPC) and artificial intelligence (AI), technological advancements must keep pace with increasing demands for speed, efficiency, and security. Synopsys recently announced the industry’s first complete PCIe 7.0 IP solution. This groundbreaking initiative addresses… Read More

Build a 100% Python-based Design environment for Large SoC Designs