As I sift through mounds of semiconductor press releases trying to figure out the relevance (with mixed results) I consider it a learning experience even when they don’t really tell me anything. This one however tells me two very important things:

1) Arm is a much more competitive company with the new leadership. I saw a noticeable… Read More

Masks have always been an essential part of the lithography process in the semiconductor industry. With the smallest printed features already being subwavelength for both DUV and EUV cases at the bleeding edge, mask patterns play a more crucial role than ever. Moreover, in the case of EUV lithography, throughput is a concern, … Read More

“Strategy” is a word sometimes used loosely to lend an aura of visionary thinking, but in this context, it has a very concrete meaning. Without a strategy, you may be stuck with decisions you made on a first-generation design when implementing follow-on designs. Or face major rework to correct for issues you hadn’t foreseen. Making… Read More

DSP and AI are generally considered separate disciplines with different application solutions. In their early stages (before programmable processors), DSP implementations were discrete, built around a digital multiplier-accumulator (MAC). AI inference implementations also build on a MAC as their primitive. If the interconnect… Read More

SoC test challenges arise due to the complexity and diversity of the functional blocks integrated into the chip. As SoCs become more complex, it becomes increasingly difficult to access all of the functional blocks within the chip for testing. SoCs also can contain billions of transistors, making it extremely time-consuming… Read More

Dan is joined by Chris Morrison, Chris has 15 years’ experience in delivering innovative analog, digital, power management and audio solutions for International electronics companies, and developing strong relationships with key partners across the semiconductor industry. Currently he is the Director of Product Marketing… Read More

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. One of those panelists was the very personable Dr. Henry Sheng, Group Director of R&D in the EDA Group at Synopsys. Henry currently leads engineering for 3DIC, advanced technology and visualization.

Are we

…

Read More

Memories have always played a critical role, both in pushing the envelope on the semiconductor process development front and supporting the varied requirements of different applications and use-cases. The list of the various types of memories in use today runs long. At a gross level, we can classify memories into volatile or … Read More

There were quite a few announcements at the TSMC Technical Symposium last week but the most important, in my opinion, were based on TSMC N3 tape-outs. Not only is N3 the leading 3nm process it is the only one in mass production which is why all of the top tier semiconductor companies are using it. TSMC N3 will be the most successful node… Read More

I’ve been following Solido as a start-up EDA vendor since 2005, then they were acquired by Siemens in 2017. At the recent User2User event there was a presentation by Kwonchil Kang, of Samsung Electronics on the topic, ML-enabled Statistical Circuit Verification Methodology using Solido. For high reliability circuits… Read More

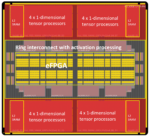

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era