Dr. Wei has served as CEO & CTO of Easy-Logic since 2020. Prior to this role, Dr. Wei served as CTO since 2014 where he constructed the core algorithm and the tool structure of EasyECO. As the CEO, Dr. Wei focuses on building a strong company infrastructure. In his CTO role he interfaces with strategic ASIC design customers … Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreGetting the most out of a shift-left IC physical verification flow with the Calibre nmPlatform

Who first came up with this term shift-left ? I’d assumed Siemens EDA as they use it so widely. But their latest white paper on the productivity improvements possible with shift-left Calibre IC verification flows puts the record straight: a software engineer called Larry Smith bagged the naming rights in a 2001 paper (leapfrogging… Read More

Democratizing the Ultimate Audio Experience

I enjoy talking with CEVA because they work on such interesting consumer products (among other product lines). My most recent discussion was with Seth Sternberg (Sensors and Audio software at CEVA), on spatial or 3D audio. The first steps to a somewhat immersive audio experience were stereo and surround sound, placing sound sources… Read More

Nominations for Phil Kaufman Award, Phil Kaufman Hall of Fame Close June 30

Plan ahead now because Friday, June 30, is the deadline to submit nominations for the Phil Kaufman Award and the Phil Kaufman Hall of Fame for anyone you think is deserving of these honors. If you haven’t given it any thought, please consider nominating someone.

Before we look at both and the nomination requirements, here’s a thumbnail… Read More

Applied Materials Announces “EPIC” Development Center

On May 22nd Applied Materials announced a new development center, Equipment and Process Innovation and Commercialization Center (EPIC).

Applied Materials already operates the Maydan Technology Center (MTC), a billion-dollar development facility with over 120 advanced process tools and 80 metrology and inspection tools… Read More

PCI-SIG DevCon and Where Samtec Fits

PCIe (peripheral component interconnect express) is an interface standard for connecting high-speed components contained in PCs, MACs and other types of processors. Think graphics, storage arrays, Wi-Fi and the like. This communication standard has become incredibly popular. The first version of the standard was released… Read More

TSMC Clarified CAPEX and Revenue for 2023!

TSMC clarified CAPEX and revenue for 2023 last night at the Annual Shareholders Meeting. Last year TSMC guided up during this meeting but this year they guided down. CAPEX was guided down to the lower end of $36B-$32B. Revenue was guided down from low-single to mid-single digit so maybe down another percent or two. The TSMC Jan… Read More

Arm 2023 Mobile Solutions Continue Gaming Focus

Arm recently announced an update for mobile under the Arm Total Compute Solutions (TCS) label, led by Chris Bergey (Sr. VP/GM for the Client line of business). You’ll remember that Chris headed the infrastructure line of business impressively through the Neoverse brand, as demonstrated by Arm-based servers appearing in multiple… Read More

Automotive IP Certification

The electrification of cars and the growth of EVs means that more semiconductor content is being added with every new vehicle model from suppliers around the globe. There are unique concerns for automotive IP in terms of reliability, security and safety over the lifetime of the vehicle. I had the pleasure to speak with Pawini Mahajan… Read More

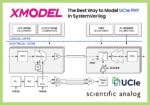

WEBINAR: UCIe PHY Modeling and Simulation with XMODEL

Join this webinar and see UCIe in action! This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center