Most MEMS and sensor companies struggle to find an industrialization partner that can support early-stage research and help develop and transition unique concepts to high-volume production. The wrong partner means delays and increased development costs as the design moves between various facilities. Recently, Silicon … Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

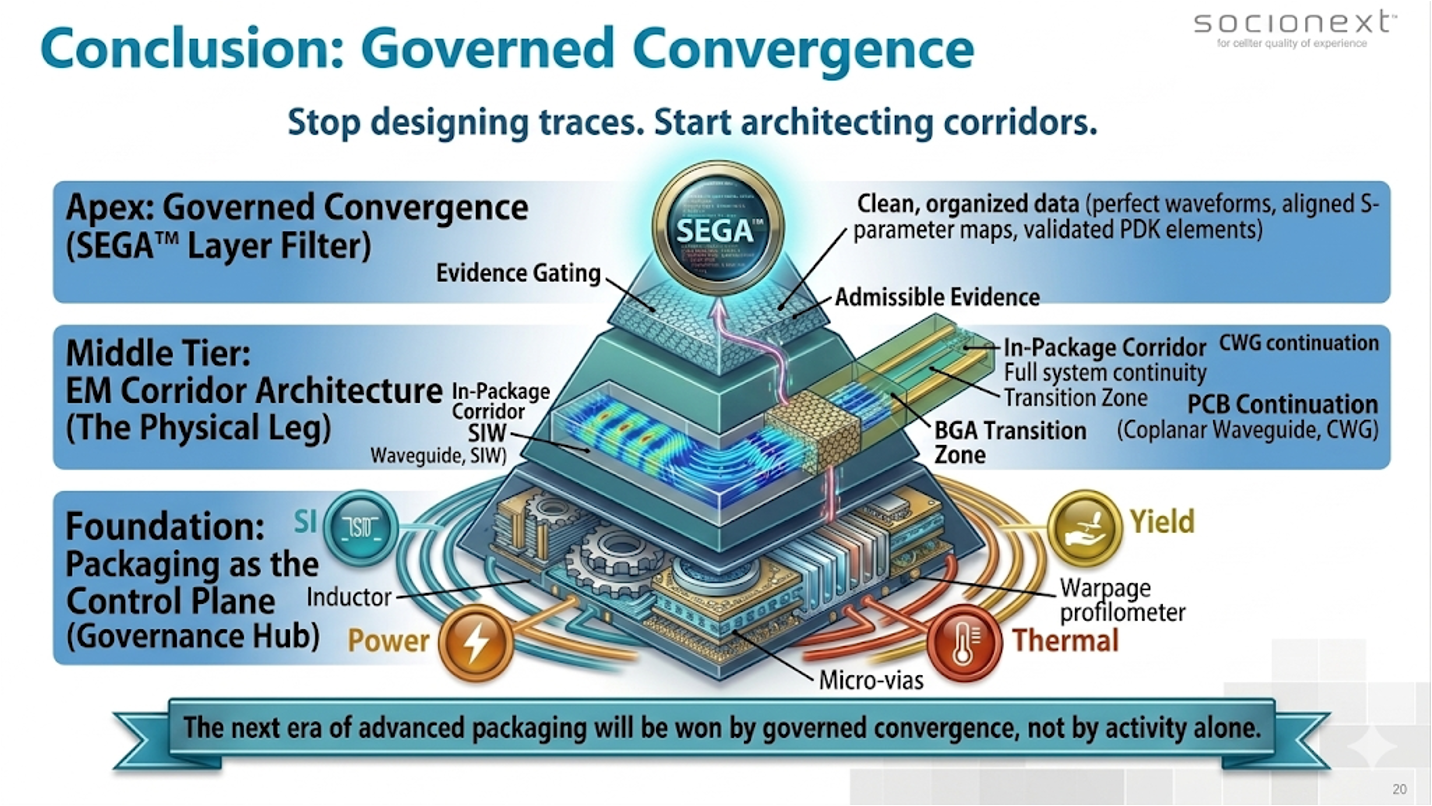

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreCEO Interview: Roger Espasa of Semidynamics

Roger Espasa is the CEO and founder of Semidynamics, an IP supplier of two RISC-V cores, Avispado (in-order) and Atrevido (out-of-order) supporting the RISC-V vector extension and Gazzillion(tm) misses, both targeted at HPC and Artificial Intelligence. Prior to the foundation of the company, Roger was Technical Director/Distinguished… Read More

Sondrel’s Drive in the Automotive Industry

Ollie Jones, Vice President of Strategic Sales at Sondrel, has worked extensively across Europe, North America and Asia and has held a variety of commercial leadership roles in FTSE 100, private equity owned and start-up companies.

Most recently Ollie was Chief Commercial Officer for an EV battery start up where he led the acquisition… Read More

A Recipe for Performance Optimization in Arm-Based Systems

Around the mid-2000’s the performance component of Moore’s Law started to tail off. That slack was nicely picked up by architecture improvements which continue to march forward but add a new layer of complexity in performance optimization and verification. Nick Heaton (Distinguished Engineer and Verification Architect at… Read More

Synopsys Accelerates Innovation on TSMC Advanced Processes

We all know that making advanced semiconductors is a team sport. TSMC can innovate the best processes, but without the right design flows, communication schemes and verified IP it becomes difficult to access those processes. Synopsys recently announced some details on this topic. It covers a lot of ground. The graphic at the top… Read More

Podcast EP223: The Impact Advanced Packaging Will Have on the Worldwide Semiconductor Industry with Bob Patti

Dan is joined by Bob Patti, the owner and President of NHanced Semiconductors. Previously, Bob founded ASIC Designs Inc., an R&D company specializing in high-performance systems and ASICs. During his 12 years with ASIC Designs he participated in more than 100 tapeouts. Tezzaron Semiconductor grew from that company, with… Read More

Tools for Chips and Dips an Overview of the Semiconductor Tools Market

From humble beginnings in military applications, the semiconductor industry has been fundamental to all societal growth, and everything that grows exponentially depends on semiconductors.

It is not a gentle industry. Products over two years old are unsellable, and there is either too much supply or none. Semiconductor scarcity… Read More

How Samtec Helps Achieve 224G PAM4 in the Real World

224 Gbps PAM4 gets attention for applications such as data center, AI/ML, accelerated computing, instrumentation and test and measurement. The question is how real is it and what are the challenges that need to be overcome to implement reliable channels at that data rate? If you wonder about these kinds of topics for your next design,… Read More

SoC Power Islands Verification with Hardware-assisted Verification

The ever-growing demand for longer battery life in mobile devices and energy savings in general have pushed power optimization to the top of designers’ concerns. While various techniques like multi-VT transistors and clock gating offer power savings at gate-level design, the real impact occurs at system level, where hardware… Read More

Anirudh Fireside Chats with Jensen and Cristiano

At CadenceLIVE 2024 Anirudh Devgan (President and CEO of Cadence) hosted two fireside chats, one with Jensen Huang (President and CEO of NVIDIA) and one with Cristiano Amon (President and CEO of Qualcomm). As you would expect both discussions were engaging and enlightening. What follows are my takeaways from those chats.

Solving the EDA tool fragmentation crisis