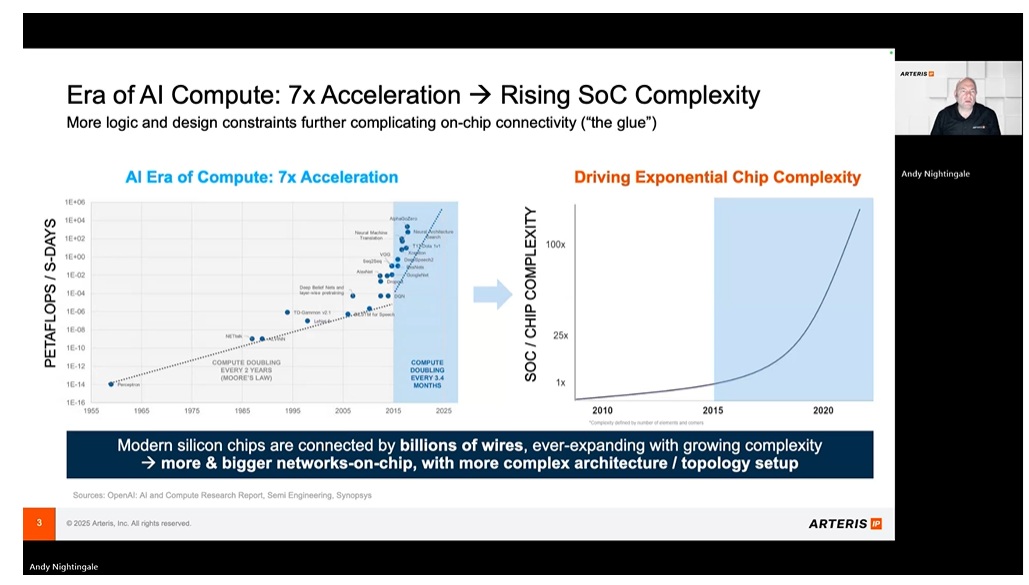

As semiconductor design pushes into increasingly complex territory, driven by Ai, ML, HPC, and heterogeneous system architectures, designers are challenged to balance performance, power, and time-to-market pressures. In this landscape, network-on-chip (NoC) architectures have emerged as a foundational building block for modern SoC interconnects, replacing traditional bus-based approaches to support scalable, high-bandwidth communication among numerous IP blocks. But designing an efficient NoC manually in an AI-ready SoC, especially with chiplet-based partitioning, quickly becomes a bottleneck. This is where Arteris Smart NoC Automation plays a transformative role.

Arteris Smart NoC Automation is a suite of tools and methodologies that automates the creation, optimization, and integration of NoC fabrics into SoC designs. Unlike conventional interconnect design flows that require extensive manual intervention, Smart NoC Automation uses intelligent, algorithm-driven processes to generate an interconnect tailored to the specific performance, throughput, latency, and area requirements of a given design. The result is a highly-optimized NoC that accelerates the path from specification to silicon, while ensuring that even the most demanding workloads, such as those driven by AI accelerators, are supported effectively.

At its core, Smart NoC Automation addresses the complexity of heterogeneous data flows within AI-ready SoCs. Modern AI workloads typically involve a diverse set of processing elements: CPUs, GPUs, AI accelerators, ISPs, and various memory subsystems (e.g., DDR, HBM). The communication patterns among these blocks are non-uniform and dynamic, requiring a flexible interconnect that can adapt to high-bandwidth data paths and low-latency control flows. Manual NoC design often results in over-provisioning (leading to wasted silicon) or under-provisioning (causing performance bottlenecks). Smart NoC Automation takes a data-driven approach, analyzing the specific traffic requirements of each block and producing a balanced network topology that meets performance goals with minimal overhead.

The transition to chiplet-based architectures further underscores the need for automated NoC design. Chiplet modular, pre-validated silicon blocks that are integrated into a system package using advanced interconnects (e.g., silicon interposers, organic substrates), enable designers to mix and match IP from different process nodes and vendors. While chiplets provide benefits such as improved yield and shorter development cycles, they complicate system integration: each chiplet may have distinct interface protocols, clock domains, and bandwidth profiles. Coordinating communication across chiplets demands a NoC fabric that can seamlessly bridge intra- and inter-chiplet domains, while maintaining coherence and meeting stringent latency constraints. Smart NoC Automation accelerates this by generating networks that are chiplet-aware, capable of mapping internal NoC segments to external interconnects with minimal designer effort.

Another key advantage of Smart NoC Automation is its ability to incorporate quality-of-service policies directly into the network fabric. AI workloads often have mixed-criticality traffic: real-time sensor data, high-volume tensor data streams, and control-plane signals all sharing the same network. Without QoS mechanisms, critical traffic can be delayed by bulk transfers, degrading performance and predictability. Automated NoC synthesis can embed traffic shaping, priority scheduling, and bandwidth reservation into the fabric, ensuring that performance-critical AI functions maintain determinism even under heavy load.

From a productivity standpoint, Smart NoC Automation drastically reduces design iterations. Traditional NoC design involves multiple manual tuning passes: adjusting topologies, re-evaluating performance models, and iterating physical design constraints. Automation compresses these cycles by generating optimized NoC proposals rapidly and enabling rapid what-if analyses. Designers can explore architectural alternatives and trade-offs interactively, without the lengthy turnaround times typically associated with manual RTL tweaking.

Finally, Smart NoC Automation supports hardware/software co-optimization, a crucial factor for AI-ready SoCs. By providing accurate performance models and exposing architectural parameters early in the design flow, software developers can optimize driver stacks, communication libraries, and scheduling algorithms in parallel with hardware development. This co-design approach ensures that both hardware and software are aligned for peak AI performance at launch.

Bottom line: Arteris Smart NoC Automation is a pivotal enabler for modern SoC design, especially in the era of AI and chiplets. By automating NoC generation and optimization, it removes one of the most time-consuming and error-prone steps in the SoC design flow, supports heterogeneous and chiplet-based architectures, ensures performance and QoS requirements are met, and accelerates overall time to silicon. As SoCs continue to scale in complexity to meet the demands of AI and next-generation compute workloads, Smart NoC Automation will remain essential for delivering high-performance, power-efficient designs on schedule.

Also Read:

The IO Hub: An Emerging Pattern for System Connectivity in Chiplet-Based Designs

Arteris Simplifies Design Reuse with Magillem Packaging

Arteris Expands Their Multi-Die Support

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.