Last week I wrote about NetSpeed’s network on chip (NoC) IP technology and design environment NocStudio. This week we see a real life application of this technology announced at CES by Imagination Technologies and NetSpeed. The companies have announced that Mobileye will use Imagination and NetSpeed IP in their next-generation ADAS and autonomous driving system-on-a-chip (SoC).

Last week I wrote about NetSpeed’s network on chip (NoC) IP technology and design environment NocStudio. This week we see a real life application of this technology announced at CES by Imagination Technologies and NetSpeed. The companies have announced that Mobileye will use Imagination and NetSpeed IP in their next-generation ADAS and autonomous driving system-on-a-chip (SoC).

Mobileye is well known for its vision accelerators for deep-layered neural networks and they have plans to use Imagination’s I6500 MIPS CPUs along with NetSpeed’s Gemini NoC IP in their next-generation SoC dubbed EyeQ5®. Autonomous driving is very compute intensive as it must deal with a myriad of simultaneous inputs to make complex real-time decisions. In 2015, Audi used a MIPs-based Mobileye SoC to complete a fully autonomous 560-mile drive from San Francisco to Bakersfield. The SoC used was the Mobileye EyeQ4®.

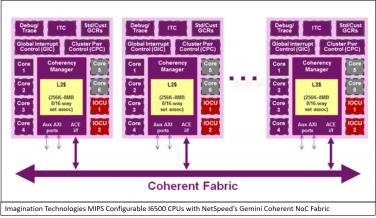

In this week’s announcement, we get a glimpse of Mobileye’s next-generation SoC, the EyeQ5®. The EyeQ5® is projected to be 8X faster than its predecessor the EyeQ4® and it is expected to produce more than 15 tera operations per second while consuming less than 5W of power. To do this the EyeQ5® will make use of a complex heterogeneous multi-core SoC that utilizes 8 configurable MIPS I6500 CPUs (the EyeQ4® used 4 MIPs CPUs) coherently combined with 18 of Mobileye’s next generation vision processors (the EyeQ4® used 6). As part of the heterogeneous I6500 clusters, NetSpeed’s Gemini NoC provides the fabric that lets Mobileye’s engineers coherently mix on-chip configurations of processing clusters for high system efficiency.

The ability to configure every component of the interconnect in a coherent heterogeneous environment is a requirement for ADAS applications. Mobileye’s designers will be able to use NetSpeed’s NocStudio software with integrated machine learning capabilities to accurately model and simulate their system configurations to optimize for the best performance, power and silicon area trade-offs and then produce fully synthesis-ready RTL for SoC implementation.

The combination of Imagination’s highly scalable MIPS I6500 CPUs with NetSpeed’s deadlock-free coherent NoC fabric enables designers to implement optimized configurations of CPU cores or clusters of CPUs. In a single cluster, designers can optimize power consumption and configure each CPU with different combinations of threads, different cache sizes, different frequencies, and even different voltage levels all while being cache coherent.

Mobileye’s use of IP from Imagination and NetSpeed IP is a valuable feather in the caps of both these IP providers as Mobileye is known to be a pioneer of heterogeneous SoC designs and they know how hard it is to get it right, especially in a coherent environment. Their SoCs are used by a majority of the world’s automakers including Audi, BMW, Fiat, Ford, General Motors, Honda, Nissan, Peugeot, Citroen, Renault, Volvo and Tesla. Mobileye’s use of these IPs is a testament to the strength of the offerings from Imagination and NetSpeed.

With 8X the computational performance of EyeQ4®, it’s easy to imagine that the EyeQ5® will take on even more data fusion than its predecessor which already simultaneously accepted inputs from 8 cameras as well as information from multiple radars and scanning beam lasers. The real power of the Imagination-NetSpeed IP collaboration, however, is that it enables Mobileye’s designers to be able to tune the additional MIPS clusters to take on more tasks while simultaneously optimizing the overall system for power, performance and cost. This could give the Mobileye team the ability to quickly configure and synthesize multiple versions of the EyeQ5® SoC architecture for different automotive markets which in turn could give them the opportunity to broaden their footprint in the automotive space and possibly take on more of the electronics functionality than just the image processing.

See also:

– Mobileye uses Imagination Technologies and NetSpeed Systems IP

– MIPS core tackles multi-core, multi-cluser designs with up to 384 cores

– NetSpeed releases Gemini 3.0 cache-coherent NoC

Solving the EDA tool fragmentation crisis