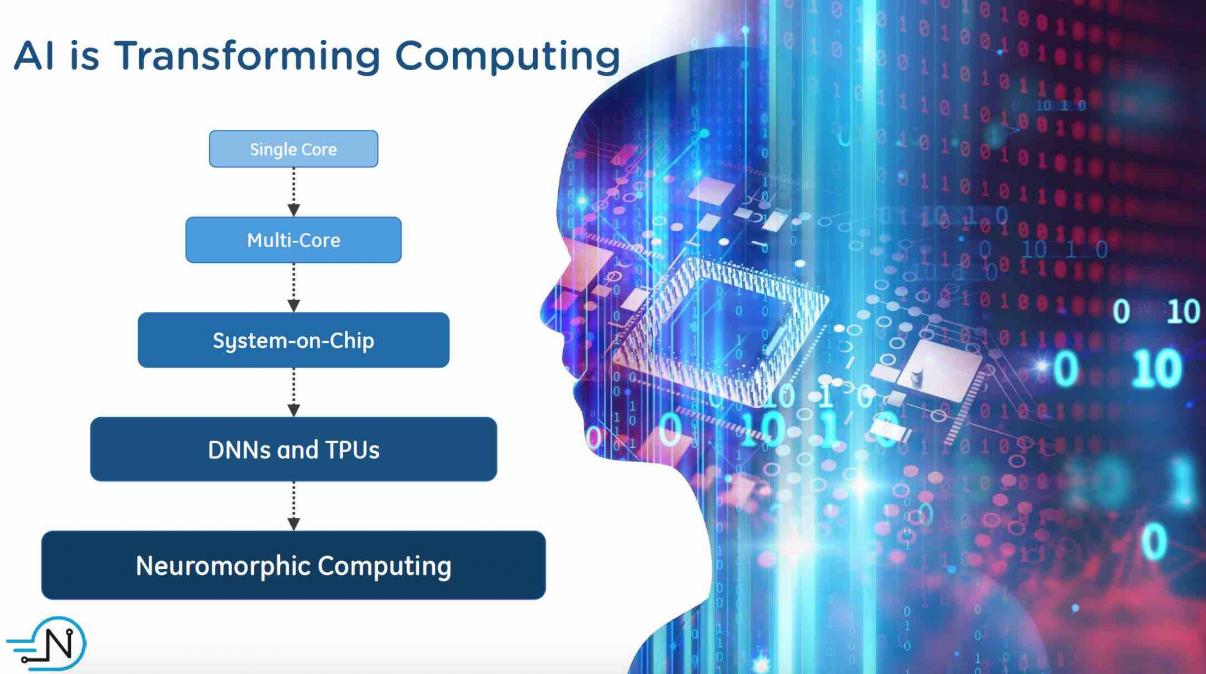

Artificial Intelligence based systems are driving a metamorphosis in computing, and consequently precipitating a large shift in SOC design. AI training is often done in the cloud and has requirements for handling huge amounts of data with forward and backward data connections. Inference usually occurs at the edge and must be… Read More

Tag: cache coherent

Machine Learning Neural Nets and the On-Chip Network

Machine learning (ML), and neural nets (NNs) as a subset of ML, are blossoming in all sorts of applications, not just in the cloud but now even more at the edge. We can now find them in our phones, in our cars, even in IoT applications. We have all seen applications for intelligent vision (e.g. pedestrian detection) and voice recognition… Read More

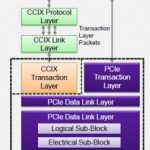

CCIX Protocol Push PCI Express 4.0 up to 25G

The CCIX consortium has developed the Cache Coherent Interconnect for Accelerators (X) protocol. The goal is to support cache coherency, allowing faster and more efficient sharing of memory between processors and accelerators, while utilizing PCIe 4.0 as transport layer. With Ethernet, PCI Express is certainly the most popular… Read More

Netspeed Gemini NoC Provides Coherent Fabric in Mobileye’s Next-generation EyeQ5 SoC

Last week I wrote about NetSpeed’s network on chip (NoC) IP technology and design environment NocStudio. This week we see a real life application of this technology announced at CES by Imagination Technologies and NetSpeed. The companies have announced that Mobileye will use Imagination and NetSpeed IP in their next-generation… Read More

It’s a heterogeneous world and cache rules it now

Cache evolved when the world was all about homogeneous processing and slow and expensive shared memory. Now, compute is just part of the problem – devices need to handle display, connectivity, storage, and other tasks, all at the same time. Different, heterogeneous cores handle different workflows in the modern SoC, and the burden… Read More

Linley Mobile and Wearable Conference Drills into Rapidly Evolving Markets

Last week the Linley conference on mobile and wearables started with an overview and keynote address by the event’s namesake Linley Gwennap. His talk offered a few surprises and was informative all around. As you have seen recently reported here on SemiWiki, he sees smartphone shipments continuing to rise, but with a declining… Read More

Arteris Unveils Solution for Heterogeneous Cache Coherent SOC’s

Designing SOC’s for markets like automotive and mobile electronics requires taking advantage of every opportunity for optimization. One way to do this is through building a cache coherent system to boost speed and reduce power. Recently, NXP decided to go about this on their automotive MCU based SOC’s by using Arteris’ just-announced… Read More

Top Mobile OEM Uses NetSpeed to Boost Its Next Gen Application Processor

The smartphone segment is certainly the most competitive market for chip makers today and the yearly product launch cadence puts a lot of pressure on the application processor design cycle. End-users expect to benefit from higher image definition, better sound quality, ever faster and more complex applications which push the… Read More

Why Gemini 2.0 is tailored for tomorrow’ SoC designs?

You probably have seen many times this graphic showing that the number of IP blocks has exploded, going from a few dozens in SoC designed in 65 nm to 120 if not more for last generation SoC targeting 16FF or 10FF. This graphic is very good at synthesizing the raw IP count, but it doesn’t tell you about another strong trend: more agents … Read More

New CoreLink IP ties in mobile GPU coherently

A mobile GPU is an expensive piece of SoC real estate in terms of footprint and power consumption, but critical to meeting user experience demands. GPU IP tuned for OpenGL ES is now a staple in high performance mobile devices, rendering polygons with shading and texture compression at impressive speeds.

Creative minds in the desktop… Read More