I met up with Andy Nightingale, VP Product Marketing and Michal Siwinski, Chief Marketing Officer of Arteris at #60DAC for an update on their system IP company dealing with SoCs and chiplet-based designs. SemiWiki has been blogging about Arteris since 2011, and the company has grown enough in those 12 years to have an IPO, see their IP used in 3 billion+ SoCs, attract 200+ customers and have 675+ SoC design starts. Their IP is used for creating a Network-on- Chip (NoC) through interconnect IP and interface IP, plus they have EDA software used for SoC integration automation.

Michal mentioned that NoC IP is growing to meet the SoC complexity demands, especially as SoC designs employ more combinations of Big and Small cores, and the process nodes get smaller. Every SoC company uses some NoC approach, even with a traditional bus approach, while NoC usage is growing the most. The average chip can now have 5-30 cores on it, and with multi-die that count could go even further. Every sub-system requires communication on chip and sees these days often multiple NoCs that help with the big challenge becomes how to integrate all of that.

Arteris stays neutral by supporting all of the popular transaction protocols, like:

- Arm, AMBA

- Ceva

- Tensilica

- OCP

- PIF

The size of the company last year was about 200, and has grown now to about 250 people, with another 30-50 reqs open. Their main R&D centers are in Silicon Valley, Austin and France.

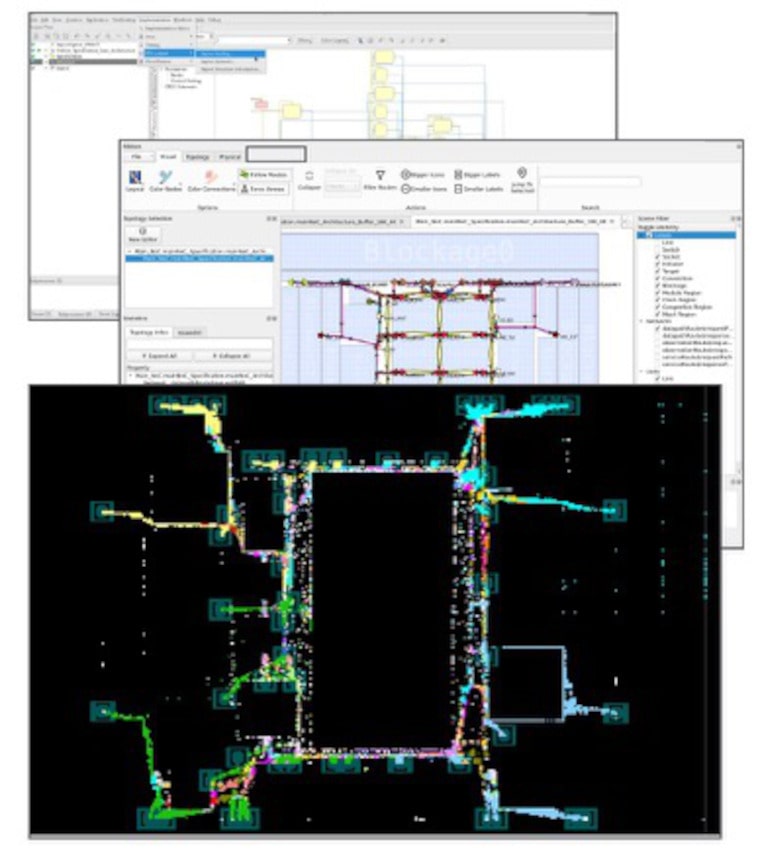

A recent release of their 5th generation of NoC added physical-awareness, with the benefit of having up to a 5X faster physical closure over manual iterations to converge. Physical effects encountered at 16nm and smaller nodes are causing respins, and these effects are so large that they need to be taken into account when placing and routing the NoC. Their new approach is to take floorplanning information and feed into the NoC creation, so that physical effects are accounted for as early as possible in the topology of the NoC.

The physical implementation works with all popular EDA tools, like Synopsys (RTL Architect), Cadence (Genus) and Siemens. Engineers run logic synthesis, P&R and static timing tools to reach their PPA goals.

Old busses simply cannot meet complexity requirements, so a NoC approach must be adopted to meet latency, power and area goals. Automotive companies and OEMs are doing their own SoC designs, and even Mercedes presented at the SNUG event this year. Early in the pandemic there were many automotive chip shortages, so that industry needs more control over their supply chain by designing their own chips.

And with the ever-rising complexity of SoCs and chipset-based designs, the NoCs integrate with the IP-XACT-based SoC integration tools that Arteris offers to customers to address that aspect of design complexity. Using the SoC integration tools, developers can re-factor RTL when new power regions need to be inserted, for instance, Arteris’ SoC integration tools stem from the acquisitions of Magillem and Semifore that Arteris did in the past.

In the ongoing AI market boom, there are notable users of Arteris IP, such as Tenstorrent for AI high-performance computing and datacenter with RISC-V chiplets, Axelera AI to accelerate computer vision at the edge, and ASICLAND for automotive, AI enterprise and AI edge SoCs.

The NoC has become a key component to SoC design, and it’s just a Smart Connector, but you really have to get it done right to enjoy the benefits. Arteris has the deep experience in this area to help your SoC team get the NoC done right.

On the chiplet front, Arteris is participating in the standards groups UCIe and CXL, so their NoC should work with any PHY choice from the popular vendors: Synopsys, Cadence, Rambus, etc.

Summary

Arteris has grown both organically, and through the complimentary acquisitions of Semifore and Magillem. Their NoC approach works with all of the interconnect standards and their IP can be used with any EDA vendor tool flow. Their presence at DAC was well received, and I look forward to watching their continued growth as a SoC system IP vendor.

Related Blogs

- Back to Basics – Designing Out PPA Risk

- Managing Service Level Risk in SoC Design

- Is Your Interconnect Strategy Scalable?

- Interconnect Under the Spotlight as Core Counts Accelerate

- Physically Aware NoC Design Arrives With a Big Claim

- Taming Physical Closure Below 16nm

- Arteris IP Acquires Semifore!

- Arm and Arteris Partner on Automotive

- Coherency in Heterogeneous Designs

Comments

There are no comments yet.

You must register or log in to view/post comments.