The recent announcement from Tabula about the $108 million raised in its Series D round of funding is putting the focus on FPGA technology, and FPGA startups in particular. Who are these FPGA startups, what is their differentiation, where is the innovation, in the product or the business model?

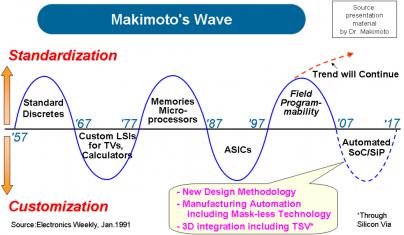

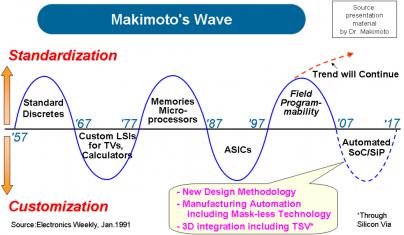

When you say FPGA, you first think: customization, “Field Programmable” means any design engineer can do it (providing he has the right tool set). Almost immediately, the two brands “Xilinx” and “Altera” come to your mind, illustrating the duopoly ruling the FPGA market. These two companies have been successful because they have been able to “standardize the customization”, by creating numerous product lines, whether low cost, or high density, or DSP centric and so on. The “Makimoto’s Wave” concept illustrates very well the expansion model of the customer specific market (ASIC, SoC, FPGA, PLD…), oscillating between customization and standardization.

If we go further, we can say that innovation, bringing by start-up, is linked with customization, and maturity with standardization. When a new product finds a market, because it offers valuable differentiation (customization) the success will pass through mass production, requiring a high level of standardization.

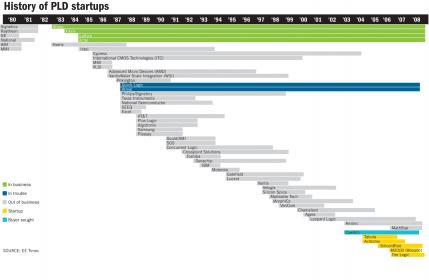

If we look at history of PLD startups (published by EETimes in July 2009) we can see that almost all the startups since 1985 are dead, except QuickLogic and Atmel, both not doing so well. We can see that the lack of money is probably not the failure reason, as the parent companies list includes AMD, Philips, TI, National Semiconductor, Samsung, SGS, Toshiba, IBM… That reminds me the person in charge of the FPGA product line for Europe for TI, in the mid 90’s, a certain Warren East. Being in charge of FPGA business may lead to success, as far as you have a chance to escape from the FPGA business, but I digress. The second statement of fact is that the companies still alive are all born after 2004. Even if we can learn a lot from post mortem analysis, we will take a look at the startups which are still alive, at their product, differentiation and business model. And try to guess who has a chance of success…

Talking about FPGA start-up, such a company has to offer a differentiated product, usually based on technical innovation, even if it can be based on a new business model, like for example offering an FPGA “design block”, or an IP, to be integrated into a more traditional SoC (ASIC or ASSP). The list of “still alive” startups is short: Achronix,Menta, Silicon Blue, and Tabula.

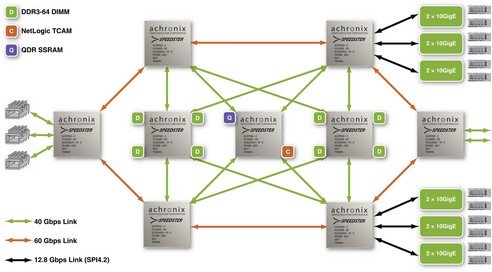

Achronix is the first FPGA to be commercially launched which is different from conventional architectures. They have developed Asynchronous FPGAs, allowing very high speed operations. Achronix claim to deliver world’s fastest FPGAs with frequencies up to 1.5GHz, Speedster family being fabricated on TSMC 65nm process. They have hard blocks for memory, multipliers, SerDes, PLLs and also for memory and communication controllers. Their CAD tools suite ACE (Achronix CAD Environment) provides a classical RTL tools flow for the programmer by hiding all the effects of Asynchronous FPGA hardware. Target market segments are networking, telecommunication, DSP, high performance computing, military and aerospace etc. The company has got special attention of industry in 2010 when they announced partnership with Intel to make 22nm FPGAs on Intel process, being the first company to share such an advanced process technology.

Differentiation: The 3H: High Speed Logic, High density, High speed SerDes

Market: Networking, high performance computing

Challenge: directly compete with the Big-2 on the sweet spot (high ASP products)

Tech./Fab:TSMC 65nm

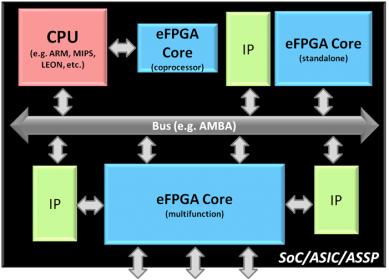

Menta licenses world’s first pure soft FPGA IP core. Having a soft IP makes its integration in a SoC very easy since it is synthesized with the standard HDL flow of design. Being a soft core the Menta’s eFPGA is technology independent, which gives a lot of easiness for SoC manufacturing since it can be integrated with any process technology for which the SoC is designed. Implementing of systems on programmable logic is slower, bigger and more power consuming compared to dedicated hardware. Menta is fully aware of this problem and its ultra compact architecture decreases this gap and helps the SoC designer to have the flexibility of FPGA with ASIC like performance.

Differentiation: Business Model (offering FPGA as an IP design block)

Market: ASSPs/ASIC, MCUs, Aerospace/Defense/Automotive

Challenge: Funding to strengthen technology and expand business

Tech./Fab: Tech. Independent!, current main focus for evaluation ST 65nm, TSMC 45nm

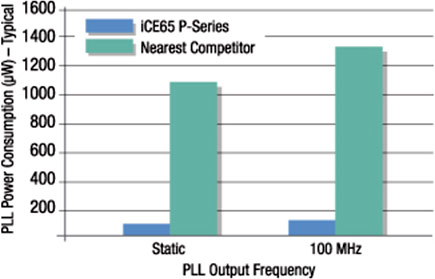

SiliconBlue has a major focus on low-power FPGAs which can be used for battery-based portable devices. Their iCE65 FPGA devices family is built on low-power TSMC 65nm process. They have done several innovations in packaging and configuration mechanism to make their devices very compact, low-power and single chip solution for the target. Their FPGAs have very low static power. Their FPGAs compared to other providers are relatively small, logic cells (LUT4+FF) range from 1200 to 16000. They have embedded memory blocks and phase-lock loops (PLL) as hard macros. They also propose their FPGAs in the form of a Die for SIP (System in Package) solutions. One of their most appreciated innovations is a single chip solution using embedded non-volatile XPM memory from Kilopass which loads the configuration to SRAMs of FPGA on power up.

Differentiation: Low power

Market: Mobile market

Challenge: meet ASIC/ASSP price point

Tech./Fab:TSMC 65nm

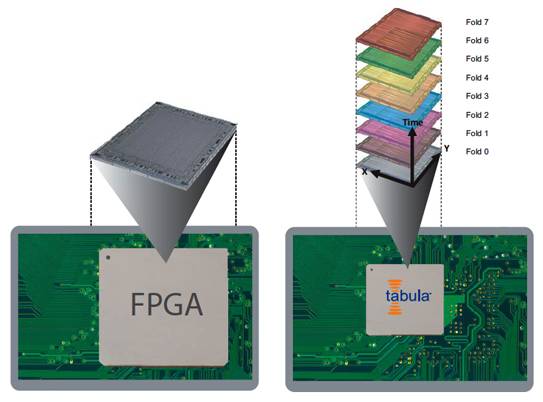

Tabula’s technology can be considered as a masterpiece of dynamic reconfiguration. The device is not physically 3D in manufacturing; they call the time as 3rd axes. By this advantage their ABAX 3PLD devices fabricated on 40nm TSMC [1.39] process when compared to an equivalent classical 2D FPGA have gains of around 2.5X in logic density, 2.0X in Memory and 3.7X in DSP performance. More importantly as stated before, despite of the architecture which is completely un-natural physically, the programming model according to the company is purely standard RTL based. Their 3D Spacetime Compiler makes this possible. Tabula claim to have Cisco as a customer.

Differentiation: Time based reconfiguration

Market: networking

Challenge:directly compete with the Big-2 on the sweet spot (high ASP products) – Product introduction has been very long (5 years+)

Tech./Fab:TSMC 40nm

These four startups are well segmented in term of differentiation: one concentrates on low complexity products offering a very low power to target the mobile industry, when the second offering high performance core logic (1.5 GHz peak performance) and supporting a wide range of communication protocols and SerDes up to 12.5 Gbps, target the Networking segment. The next two proposes real disruptive innovation: the third proposing to embed FPGA as a design IP block (business model innovation), targeting IDM or Fabless in multiple segments, when the fourth has created the “3 D” FPGA concept where the 3rd dimension is the time.

To be honest, none of these startups should “loose”, as each of them is offering a key differentiator. Except if they fail to attract customer because of too complex design flow or too expensive toolset, of fail to keep them because of wrong execution (in production). Or simply if the duopoly can close the technology gap. We will probably dig more and come back in a next blog, as this is a fascinating part of the SC industry.

I would like to thank Syed Zahid Ahmed (www.linkedin.com/in/SyedZahidAhmed) who has helped me to write this blog, using the know how of the emerging FPGA market acquired when doing research for his PhD. . By the way, Zahid will defend his PhD in June, and is looking these days for his next adventure (job)!

Eric Esteve (eric.esteve@ip-nest.com)

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center