No matter how impressive the specifications are for an SoC, the power performance and area of the finished design all depend on the IP selected for the IO blocks. In particular, most SOCs designed for consumer and enterprise applications rely heavily on PCI Express. Because PCIe analog IP is critical to design success, Samsung has developed a solid relationship with the IP provider Analog Bits that was highlighted in a talk given by Analog Bits Executive VP Mahesh Tirupattur at the recent Samsung Advanced Foundry Ecosystem (SAFE) Forum. The talk is titled “PCIe/CXL SERDES- Gen4/5 Enterprise Class Serdes & Lowest Power Gen3/4 Consumer SERDES in Samsung 28nm to 5nm Processes”. Mahesh offers extensive information on their SERDES IP on Samsung processes from 32nm in 2012 up the present with their 7LPP and 5LPE support in 2021.

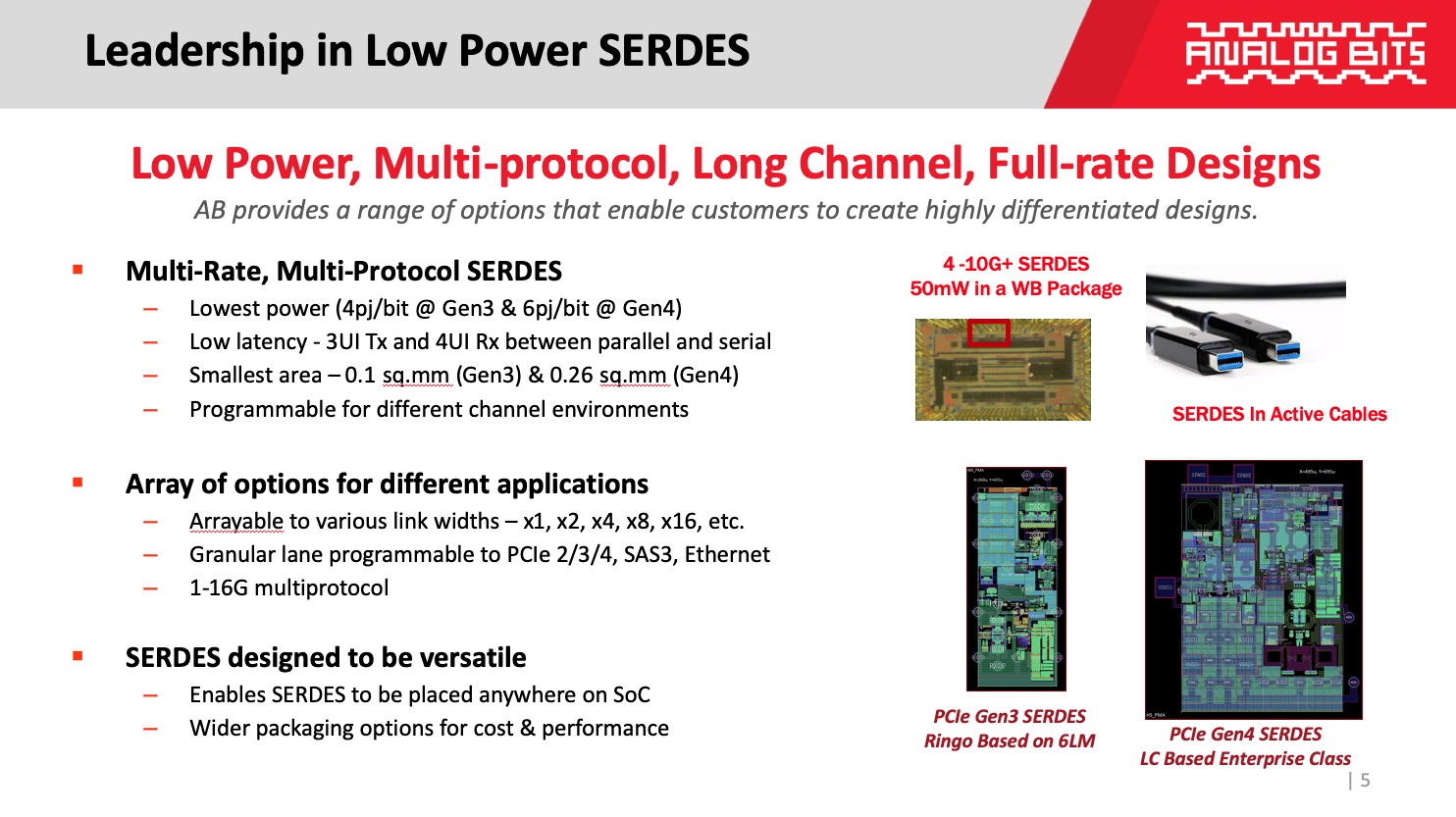

According to Mahesh, their primary focus is in helping their customers to create highly differentiated designs targeted at customer needs. To this end they focus on low power, small silicon footprint and flexible configurations, among other things.

For the consumer market, Analog Bits delivers PCIe Gen2 and Gen3 with multiprotocol ability for SATA, eDP, XFI, etc. Their full rate architecture offers industry leading picojoules per bit combined with the lowest system and BOM cost. They support wire bond packages (up to 10G) and integration with clock chips. Their small form factor lowers silicon costs. Lastly, they include some programmability to the supported protocols.

Their enterprise and high performance PCIe SERDES offer Gen4/5 and extensibility to support SAS4, Ethernet, etc. Designs can have lane counts of 195 to over 300 placed on all multiple sides. They offer automotive grades and provide multiple channel and chassis support with channel equalization. These SERDES have been used in data center storage, GPUs, aggregators, bridges, re-timers and AI/ML.

Analog Bits’ PCIe SERDES can be arrayed to varying link widths, i.e. x1, x2, x4, x8, x16. Lanes can be independently programmed to support any PCIe spec, SAS, Ethernet, etc. They also offer flexibility for placement anywhere on an SOC and wider packaging options to improve cost and performance. One of his slides highlights the low power obtained for PCIe Gen3 in 28 FDSOI and 28LP Bulk. Coming in at 0.1 sq mm they both have similar PCIe power and dynamic power, ~54mW and ~6.8 mW/Gbps respectively. The FDSOI leakage of 30.5 microWatts betters the LP Bulk at 46.6 microWatts.

Mahesh spends some time discussing sample layouts for low power SERDES in wire bond packages. He includes test result eye diagrams at 5Gb/s, 8Gb/s and 10Gb/s that all look wide open and clear. Even the eye diagram for the high-performance full rate PCIe Gen4 SERDES that is used on Samsung NVMe SSD is impressive. It uses 117.7 mW per lane at 16Gbps (7.35mW/Gbps) in an area of 0.26 sq. mm.

Analog Bits has silicon proven test chips and also production tape outs for their Gen3 and Gen4 SERDES on Samsung 7LPP/5LPE. The Gen4 silicon is 1-16G with power coming in at 6 pj/bit. The Gen 3 is 1-8G with power at 4pj/bit. Gen5/SAS4 is on Samsung 8LPP with working silicon. Its stats are 0.583 sq. mm and 7.6 pj/bit, and is configurable across multiple lanes.

The presentation goes into extensive detail on test results and available layout configurations. I highly recommend the presentation because of the level of detail that it provides. Analog bits has a long term history developing IP for the full range of Samsung processes. As noted above it is impressive that Samsung chose Analog Bits to provide SERDES IP for their own NMVe. The presentation is available at analogbits.com/analog-bits-pcie-cxl-serdes-in-samsung-video/

Also Read:

On-Chip Sensors Discussed at TSMC OIP

Package Pin-less PLLs Benefit Overall Chip PPA

Analog Sensing Now Essential for Boosting SOC Performance

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.