Memory testing in the early days of computing was a relatively straightforward process. Designers relied on simple, deterministic approaches to verify the functionality of memory modules. However, as memory density increased and systems became more complex, the likelihood of faults also rose. With advancements in memory technologies, more sophisticated testing strategies emerged. Error correction codes were introduced, and self-repair strategies were developed alongside increasingly automated methods.

I spoke with Pawini Mahajan, Sr. Staff Product Manager, Memory Test & Repair Solutions at Synopsys to discuss the evolution of memory test and repair. The discussion also touched on the impact of AI-driven workloads, the challenges introduced by modern memory technologies, and the features and approaches needed for effective solutions.

The Evolution of Memory Test and Repair

Historically, memory test and repair techniques were designed for simpler architectures. As semiconductor technology advanced, memory densities increased, requiring more sophisticated test and error correction mechanisms. A notable advancement was the introduction of Built-In Self-Test (BIST) techniques, which allowed memory systems to test themselves autonomously. BIST mechanisms integrated test patterns into the memory’s design, enabling self-diagnostics during operation. This capability reduced the need for external testing and provided a more robust way to identify memory faults before they caused significant system failures.

A major breakthrough came with the introduction of the Synopsys STAR Memory System™ (SMS), which revolutionized memory test and repair technology in the industry. Yervant Zorian, the Chief Architect and Fellow at Synopsys, was the visionary behind this breakthrough. SMS provides integrated BIST, error correction, redundancy allocation, and self-repair functionalities, making it a game-changer for embedded memory solutions. Unlike earlier solutions, SMS offers continuous monitoring, identifying potential problems before they escalate into system failures. If a fault is detected, SMS can automatically apply redundant memory mappings or other repair strategies to ensure system functionality without requiring a restart or manual repair. This innovation significantly improves manufacturing yield, in-field reliability, and system-level performance.

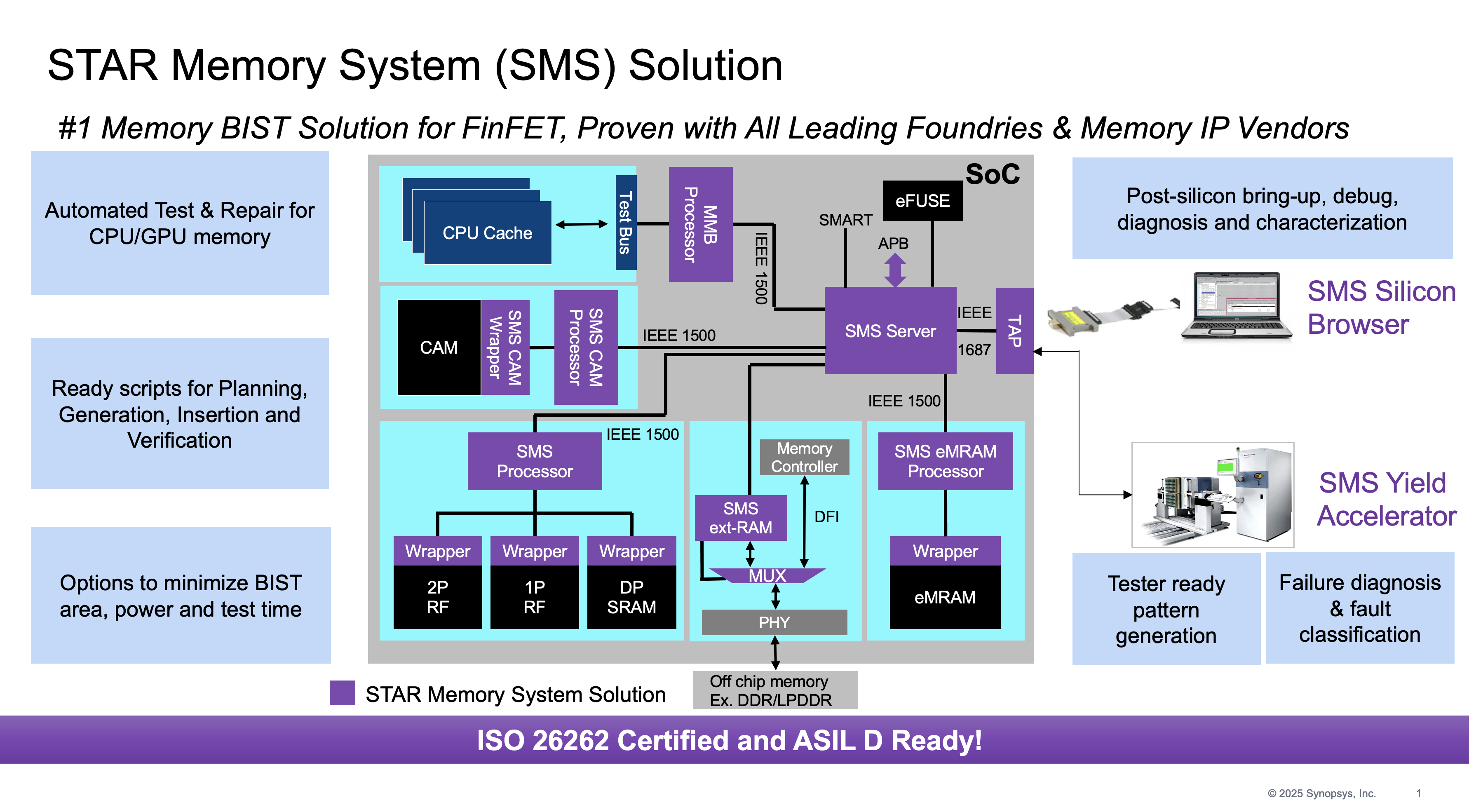

Synopsys STAR Memory System (SMS)

The Synopsys SMS is a comprehensive, silicon-proven test, repair, and diagnostics solution designed for both Synopsys and third-party memories. It incorporates a test wrapper around each memory instance, enabling controlled access during test mode. These wrappers connect to the SMS processor, which handles test execution, failure diagnosis, and redundancy analysis. The system automates the integration of test and repair IP at the RTL level, ensuring correct connectivity through automated test-bench verification. The SMS processor interfaces with the SMS server via the IEEE 1500 standard, utilizing a TAP controller for test access and scheduling. Additionally, SMS generates tester-ready patterns in STIL, WGL, or SVF formats and features advanced diagnostics that allow SoC designers and test engineers to pinpoint the exact physical location of failing bitcells. Furthermore, SMS provides interactive silicon debugging capabilities in a lab setup without requiring a production tester, streamlining the debugging process and accelerating time-to-market.

Challenges Introduced by Modern Technologies

The rapid advancement of computing, particularly with the rise of AI-driven workloads, has significantly reshaped the landscape of memory test and repair. Traditional memory architectures are being replaced with high-performance solutions such as High Bandwidth Memory (HBM) and Compute High Bandwidth Memory (cHBM) to meet the demands of modern applications. However, these advancements introduce new challenges in defect detection, repair strategies, and real-time optimization.

Modern technologies, such as Gate-All-Around (GAA) and multi-die systems, have also significantly increased the complexity of memory design and testing. These advanced architectures, with densely packed memory configurations, heighten the risk of faults, making traditional testing methods insufficient. New fault types introduced by these technologies are difficult for conventional algorithms to detect. Additionally, multi-die architectures complicate fault isolation and repair, and the scale of memory required for AI/ML workloads, such as HBM and cHBM, makes comprehensive testing increasingly difficult. As systems operate under heavy workloads, particularly in cloud or edge environments, traditional offline diagnostics are inadequate. There is a growing need for in-field diagnostics and self-repair capabilities to minimize downtime and ensure continuous performance. Moreover, the reuse of design IPs for faster time-to-market creates challenges in ensuring compatibility and reliability within new memory configurations.

Approaches to Address These Challenges

To tackle these challenges, modern memory systems must employ several advanced features. On-chip memory diagnostic (OCMD) capabilities enable real-time fault monitoring without external testers, which is particularly useful for AI/ML applications. For multi-die systems, SMS pattern diagnosis and debug capabilities help address the complexities of interconnected chiplets. Additionally, quality-of-results (QoR) optimization ensures high-performance memory for demanding workloads. Flexible repair hierarchies allow for efficient, targeted repairs without disrupting the entire system, and special testing methods are used to address defects in abutted designs, which maximize silicon area. Native IEEE 1687 support ensures seamless integration of testing across all components, while APB integration allows for comprehensive diagnostics across different memory hierarchy levels. Finally, features such as configurable e-fuse drivers and support for specialized memory types, such as banked memory, enable flexible adjustments to enhance performance and fault tolerance. Together, these solutions ensure that memory systems can meet the performance and reliability needs of next-generation computing.

The Future of Memory Test and Repair: AI-Integrated Systems

As memory demands continue to grow, the need for real-time fault detection, repair, and optimization will only become more critical. The SMS’s ability to seamlessly integrate with modern AI workloads ensures that it will continue to evolve and meet the needs of cutting-edge systems. The next phase will involve integrating AI and ML even further into memory management, enabling intelligent fault prediction, self-optimizing repair strategies, and enhanced performance monitoring. These advancements will ensure that future memory architectures can sustain the increasing computational demands of AI-driven applications.

Watch for Synopsys announcements later this year, extending and expanding their SMS solutions addressing AI-driven workloads.

To learn more about Synopsys STAR Memory System solution, click here.

Also Read:

DVCon 2025: AI and the Future of Verification Take Center Stage

Synopsys Expands Hardware-Assisted Verification Portfolio to Address Growing Chip Complexity

How Synopsys Enables Gen AI on the Edge

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.