The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target problems on the rise as designs become more complex and use more disparate IP blocks: incompleteness, and a lot of iterations. Rather than sit around and wait for all the IP blocks and accurate constraints, the value of early design exploration – first pass looks at floorplan and area, routing congestion, power, and other important factors – running with what is known is becoming more common for productivity reasons.

Previewed today, Synopsys Design Compiler 2013.12 continues to target problems on the rise as designs become more complex and use more disparate IP blocks: incompleteness, and a lot of iterations. Rather than sit around and wait for all the IP blocks and accurate constraints, the value of early design exploration – first pass looks at floorplan and area, routing congestion, power, and other important factors – running with what is known is becoming more common for productivity reasons.

The traditional cycle in dealing with complex designs has a lot of long iterations back and forth between the front end and back end design teams, but the missing pieces can have a curious effect on designer behavior. “What people started to do is if their net delays weren’t accurate enough, they would overconstrain the design and timing,” Vijayvargiya observes. That approach to trying to limit iterations reduces place and route risk, but results in overuse of area and power.

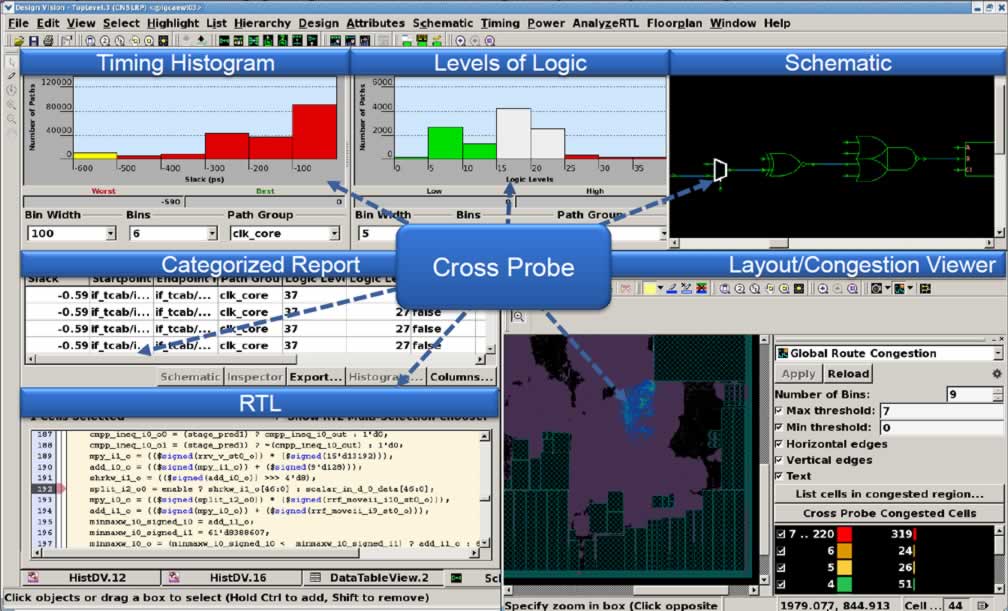

Early exploration can help direct efforts to problem areas sooner in the cycle, reducing guessing and wasted effort in excessive iterations. Both DC Explorer and Design Compiler Graphical, existing tools in Design Compiler, can look at and visualize routing congestion. DC Explorer is meant to improve the quality of constraints and can detect unrealistic or missing ones during synthesis, and provides a categorized timing report to show how much margin exists and where violations are occurring. Design Compiler Graphical is an implementation tool and tries hard to meet the constraints, but helps visualize where problems like “missing” false or multi-cycle paths exist.

Synopsys Design Compiler 2013.12 builds on these ideas with three new improvements:

1) 10% reduction in area and leakage power, at all process nodes. This is an interesting claim, for a couple of reasons. Obviously new designs benefit, but Vijayvargiya emphasizes this applies to legacy designs, running against an existing netlist gate-to-gate without impacting timing, which could result in a cost savings by reducing die size. She was also refreshingly honest about the difficulty and development time involved for this effort, saying 10% was the goal – the current release delivers 5%, and Synopsys is working on a planned Service Pack update coming in March to deliver the other 5%.

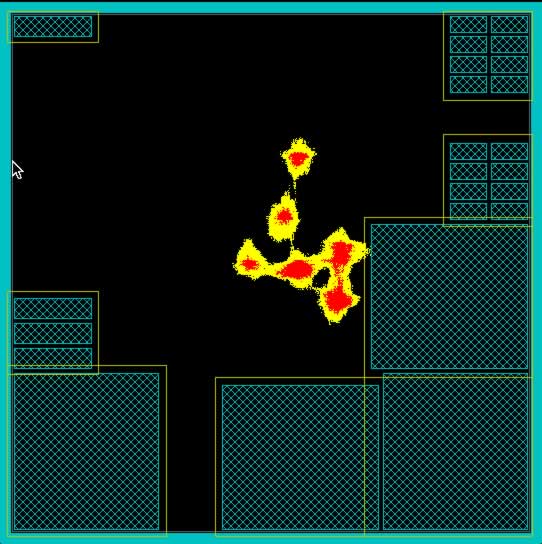

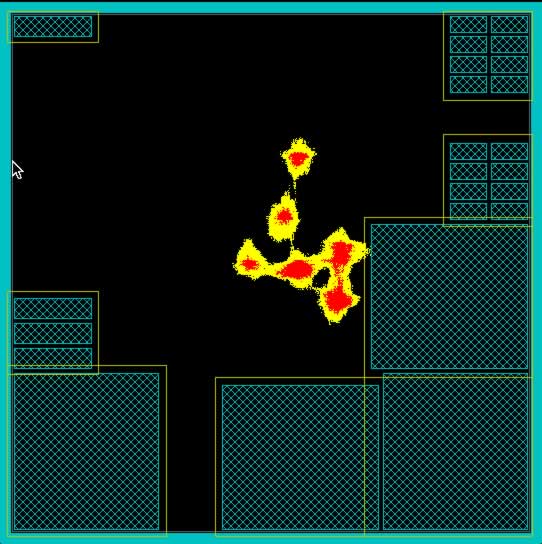

2) Early congestion detection and optimization. In DC Explorer, new capability is available to view any congested regions, and cross probe those over to other design views so the source of the problem is clear. This can help ease the iteration process, removing much of the guesswork for the RTL team in making modifications to help place and route succeed. Views include path slack histograms, path logic levels, the RTL code, the schematic, and the floorplan.

3) Golden UPF support.The Unified Power Format has been a boon for designers, a standardized format defining power intent at RTL. Previously, synthesis optimized RTL creating a netlist, and in the process may have altered some names found in the UPF file – creating what Vijayvargiya called “UPF Prime” which was used throughout. Now, Design Compiler creates a supplemental file and rechecks against the original unaltered “golden” UPF file throughout the flow, increasing fidelity to what designers specified and providing automated traceability.

For official commentary on these improvements, Synopsys has posted their insight:

Latest Release of Design Compiler Adds Technologies to Reduce Area and Accelerate Design Schedules

When it comes to bet-the-farm EDA back end automation, part of the trick is dealing with unknowns without overcompensating or guessing, providing insight as to where relief is likely needed. Wringing out 10% in area and power and providing visibility to snags that can trip design schedules within a familiar environment is a solid accomplishment for the Synopsys teams.

More Articles by Don Dingee…..

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.