Breker has been in the system test synthesis game for 12 years, starting long before there was a PSS standard. Which means they probably have this figured out better than most, quite simply because they’ve seen it all and done it all. Breker is heavily involved in and aligned with the standard of course but it shouldn’t be surprising… Read More

Tag: constraints

Breker on PSS and UVM

When PSS comes up, a lot of mainstream verification engineers are apt to get nervous. They worry that just as they’re starting to get the hang of UVM, the ivory tower types are changing the rules of dynamic verification again and that they’ll have to reboot all that hard-won UVM learning to a new language. The PSS community and tool … Read More

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

Design units come to faster Riviera-PRO release

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

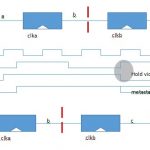

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

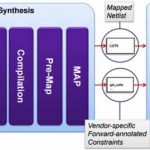

Understanding QoR in FPGA synthesis

We’ve all heard this claim: “Our FPGA synthesis tool produces better quality of results (QoR).” If you’re just hoping for a tool to do that automagically, you’re probably doing it wrong. Getting better QoR depends on understanding what an FPGA synthesis tool is capable of, and how to leverage what it tells you.… Read More

Untangling snags earlier and reducing area by 10%

The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target … Read More

The never-ending quest to kill metastability

The difficulty of an engineering problem can be gauged by two things:

1) The number of attempts to generate a solution.

2) The degree of hyperbole used to describe the effectiveness of the latest solution.

The problem many folks in the EDA industry are after right now is clock domain crossings (CDCs) and the resulting metastability… Read More

Analog Constraint Standards

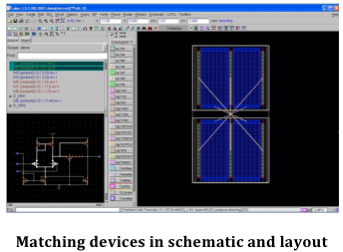

Over the years there has been a lot of standard creation in the IC design world to allow interoperability of tools from different vendors. One area of recent interest is interoperable constraints for custom IC design. Increasingly, analog design layout is becoming more automated. Advanced process nodes require trial layouts… Read More