There is a lot more to sound than meets the ear, and there a vast number of ways to deliver an audio experience. I recently trashed my gaming headset, replacing it with a Samson C03U mic and Audio-Technica ATH-PRO700MK2 headphones. It’s a huge upgrade, especially for podcasting, and I admit I was also motivated by research into digital music formats. Audio is fascinating, and I enjoy learning about how it works.

My counterparts here at SemiWiki have written extensively about CEVA and Tensilica who dominate the audio DSP IP space, which includes a few others like ARC (now part of Synopsys), Imagination Technologies, and VeriSilicon. Those cores implement the digital processing part of audio, which depending on the standard and algorithms involved can be serious heavy lifting. But, they still require analog interfacing.

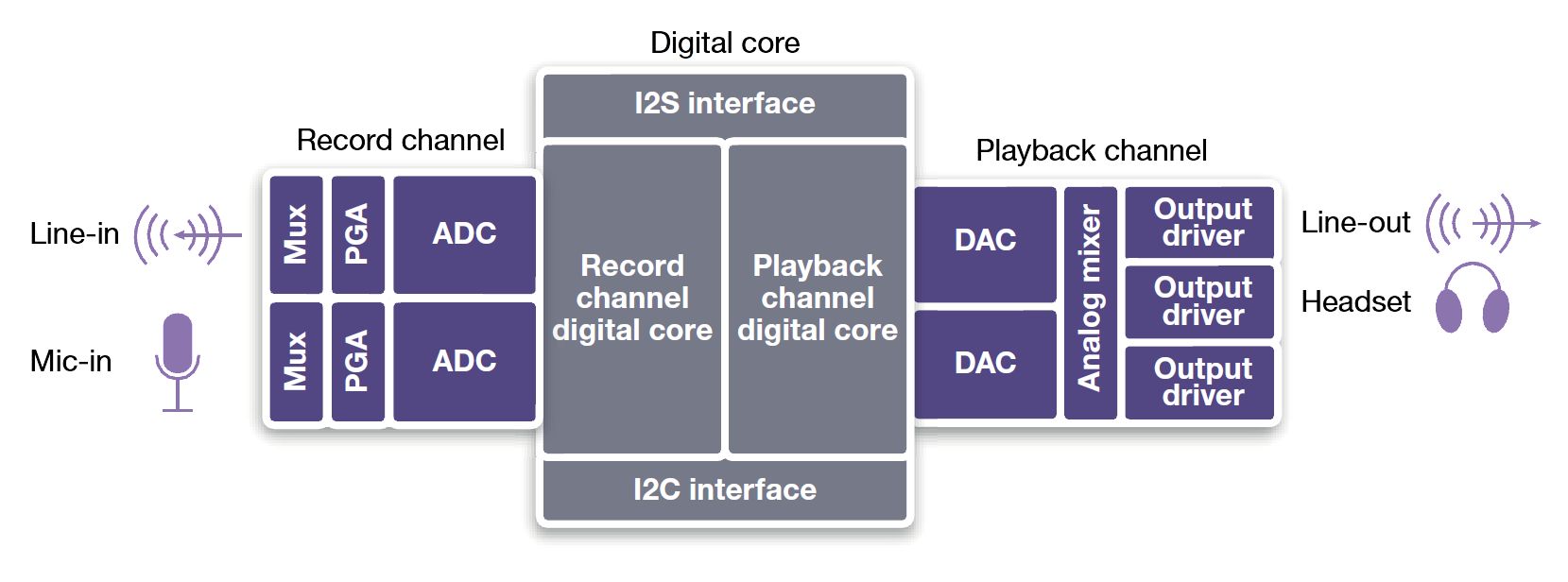

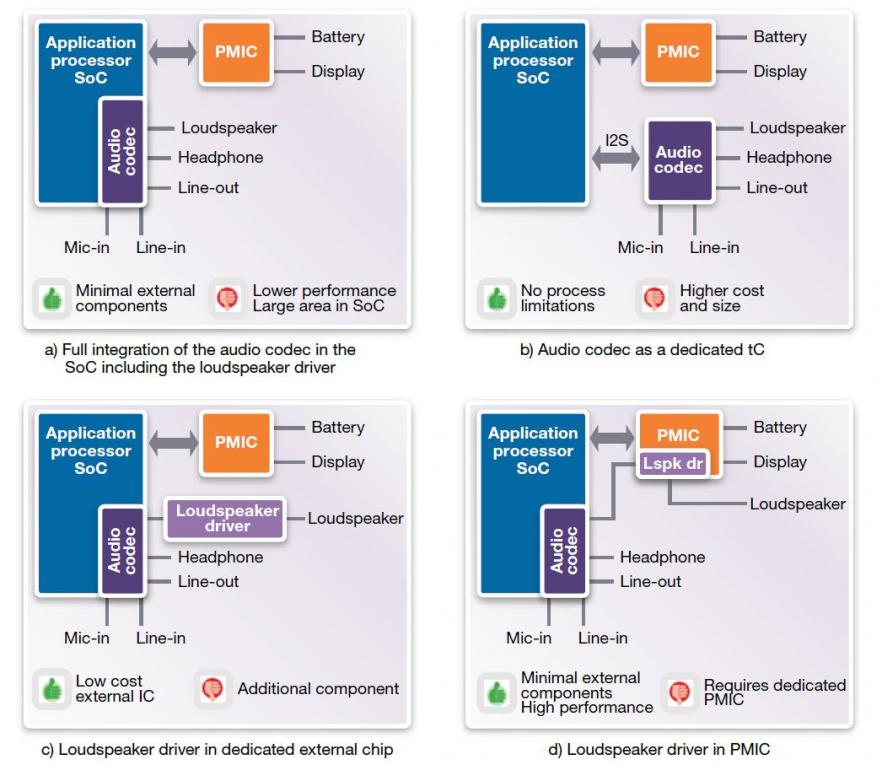

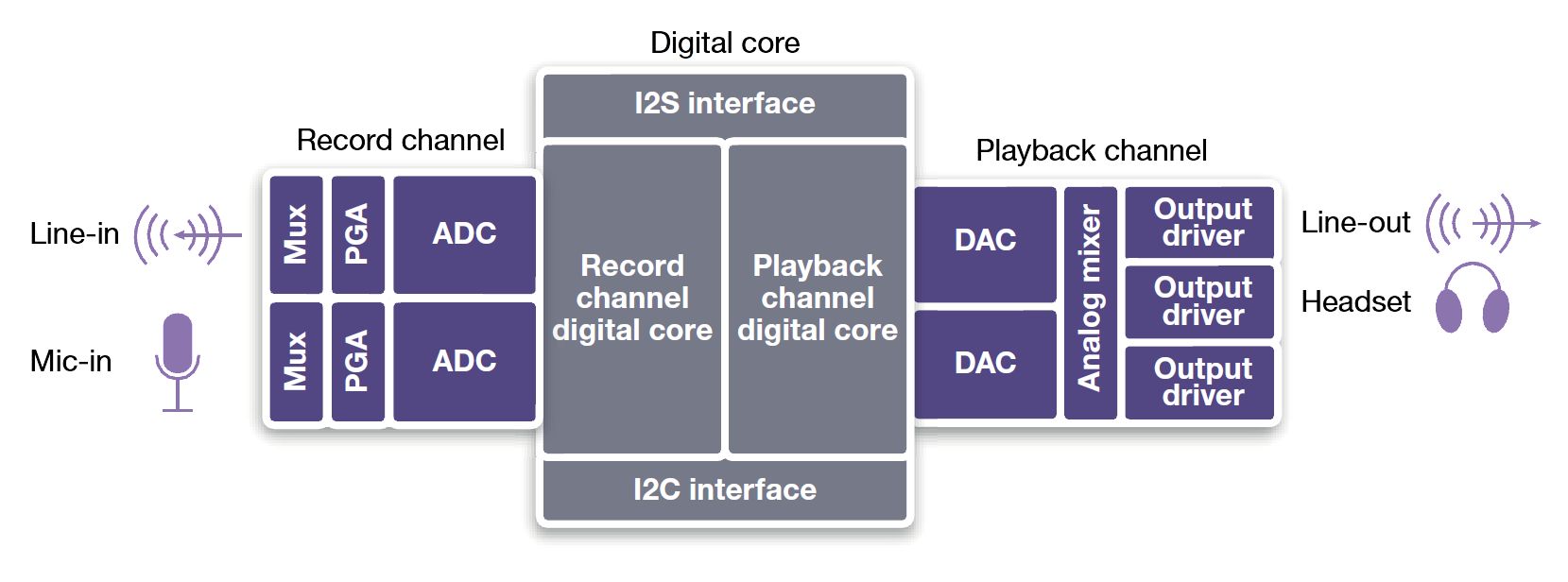

Those cores and others have been worked into a vast array of “audio codec” devices, including parts from Analog Devices, Conexant, IDT, TI, Toshiba, Wolfson, and others. These parts combine the analog conversion, multiplexing, filtering and more with digital processing, often providing an I2S interface to the application SoC. While these ports can offer excellent performance in the areas of dynamic range, signal-to-noise ratio (SNR), and total harmonic distortion (THD), they add to system complexity and cost and space of a separate device.

Analog designs are also notoriously finicky, requiring care in layout and careful handling of clocking, power, and signal matching. This is one possible use of 3D – dropping an analog circuit in a mature process node wholesale into a more aggressive digital layout, preserving the meticulous attention to noise reduction and other issues.

Synopsys is looking to leverage their analog experience and provide a direct solution for 28nm, with their DesignWare Premium Audio Analog Codec IP. By capturing an analog design in hard IP, they solve many of the concerns digital designers normally have with analog layout. The design combines 24-bit analog-to-digital and digital-to-analog conversion, with better than 96 dB dynamic range on the DAC.

Such a good dynamic range figure is remarkable, given the increased susceptibility to noise in analog circuitry as geometries shrink – standalone audio analog codecs are nowhere near 28nm with good reason. Perhaps more interesting than the IP itself are several other unique issues in audio integration in advanced SoCs, outlined in a white paper authored by Carlos Azeredo-Leme and Craig Zajac.

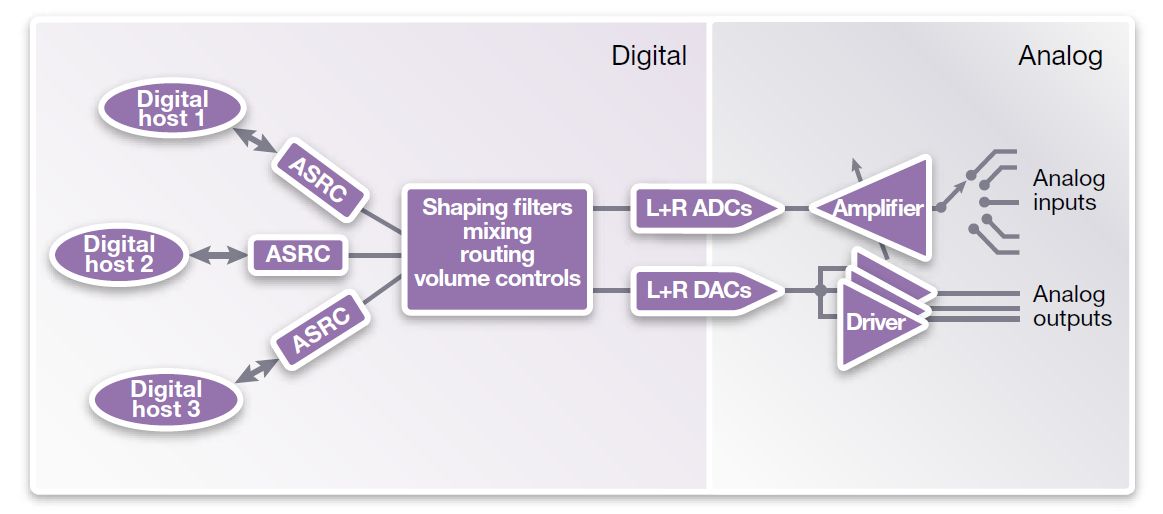

Dealing with multiple audio channels with different clocks and sample rates. The big enhancement the Synopsys Premium Audio Analog Codec IP offers is an asynchronous sample rate converter (ASRC), which allows multiple audio streams to be multiplexed into a single stream re-sampled with a common clock. This also reduces the complexity of filtering, mixing, and volume control operations by allowing them to work on the converged stream.

Working with reduced supply voltages. Designers faced with a 1.8V power supply have a limitation driving audio for headphones at a typical power level of 40 mW – the result is more like 11 mW, which some implementations might be happy with. To get more power, designers might want to look at creating a -1.8V rail using a charge pump design.

Driving larger external speakers. One thing the authors didn’t mention was this use case is actually diminishing with Bluetooth-paired speakers gaining popularity, but sometimes a physical connection is still preferred. Instead of using an entire standalone audio codec, just a speaker power amplifier can be implemented.

In other words, there are a lot of choices in audio implementation related to the analog subsystem, which cause examination of issues beyond the choice of digital audio processing. By creating the possibility of direct integration of analog functions on an advanced 28nm process, designers can meet many requirements with a higher level of integration and reduced system cost. It is worth understanding the tradeoffs involved.

You can learn more on the Synopsys IP and the implementation issues:

Datasheet: Premium Audio Analog Codec IP

White paper: Implementing Audio Codecs in 28-nm Mobile Multimedia Advanced SoCs

Comments

There are no comments yet.

You must register or log in to view/post comments.