At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

Electronic Design Automation

Aldec Verifies Compatibility of Northwest Logic’s PCI Express Cores with HES-7™ SoC/ASIC Prototyping Platform

Henderson, Nevada – July 11, 2013 –Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification solutions, today announced that engineers incorporating high-speed PCI Express data transmission into their SoC and ASIC designs can accelerate their time-to-market utilizing Northwest Logic… Read More

Data Centers accounts for 2 to 3% of WW Energy Consumption!

Do you think this figure will go down? Considering the massive move to Mobile equipment, pushing to de-localize your storage medium to instead use the cloud capabilities, and looking at the huge number of people buying smartphone and tablet in emerging countries, no doubt that Data Center related energy consumption is expected… Read More

Analysis of HLS Results Made Easier

In a recent article I discussed how easy it was to debug SystemC source code as shown in a video published on YouTube by Forte Design Systems. I also commented on the usefulness of the well-produced Forte video series. Today, I am reviewing another video in that series on analyzing high-level synthesis (HLS) results.

Cynthesizer… Read More

A Goldmine of Tester Data

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More

Best Practices for Using DRC, LVS and Parasitic Extraction – on YouTube

EDA companies produce a wealth of content to help IC engineers get the best out of their tools through several means:

- Reference Manuals

- User Guides

- Tutorials

- Workshops

- Seminars

- Training Classes

- Phone Support

- AE visits

Towards the 0 DPM Test Goal

At Semicon yesterday I attended Mentor’s presentation on improving test standards. Joe Sawicki was meant to present but he was unable to get a flight due to the ongoing disruption at SFO after last weekend’s crash. I just flew in myself and it is odd to see the carcase of that 777 just beside the runway we landed on.

The … Read More

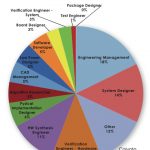

Calypto 2013 Report

Each year Calypto runs a survey of end-users. This year’s survey and report has two parts, power reduction and high level synthesis (HLS).

The topics covered are:

- survey methodology and demographics

- top methods used to reduce power

- engineering time spent on specfiic RTL tasks to reduce power

- plans to deploy RTL power reduction

Easy SystemC Debugging

Electronic system design has been slowly migrating to higher level languages such as SystemC for more than a decade now. SystemC is an open source C++ library that has emerged as a standard for high-level design and system modeling. Writing code in SystemC has several advantages which I won’t elaborate on in this article, though… Read More

LicenseMonitor Users’ Group Silicon Valley

If DAC is the most general event in our industry, then the LicenseMonitor Users’ Group Silicon Valley has to be one of the most focused. It was held back in May but one of the key presentations was Brian Janes of RTDA talking about what is new in the latest version of LicenseMonitor which is 2013.03.

Like a number of people at RTDA,… Read More

Is Intel About to Take Flight?