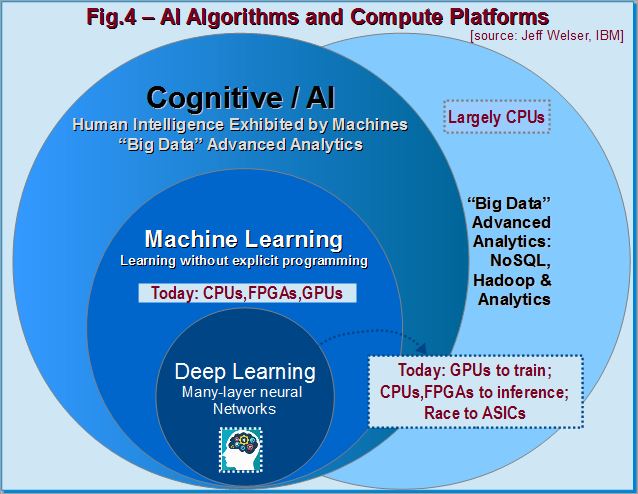

Adding color to the talks, Dr. Jeff Welser, VP and IBM Almaden Research Lab Director showed how AI and recent computing resources could be harnessed to contain data explosion. Unstructured data growth by 2020 would be in the order of 50 Zetta-bytes (with 21 zeros). One example, the Summit supercomputer developed by IBM for use at… Read More

Electronic Design Automation

Qualcomm, AMD on Verification with Synopsys

Synopsys hosts a regular lunch at DVCon each year (at least over the last few years I have checked), a nice meal and a show, opening a marketing update followed by 2-3 customer presentations on how they use Synopsys verification in their flows. This year’s event was moderated by Piyush Sancheti from Synopsys Verification marketing… Read More

Siemens Leverages Mentor Embedded IoT Framework for Industry 4.0

For those of you who wondered at the logic behind Siemens acquisition of Mentor Graphics last year, look no further than a recent announcement by Mentor, now a Siemens business, regarding the release of their new Mentor Embedded IoT Framework (MEIF). To help connect the dots, we need to back up a bit and review a few things about how… Read More

Free Webinar: Silvaco 3D Solver Based Extraction for Device and Circuit Designers

Designers spend a lot of time looking at their layouts in 2D. This is done naturally because viewing in 2D is faster and simpler than in 3D. It helps that humans are good at extrapolating from 2D to 3D. Analysis software, such as extraction software also spend a lot of time looking at layouts in 2D. While this is fine for approximate results,… Read More

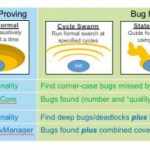

Formal: Going Deep and Going Early

This year I got a chance to talk with Cadence at DVCon on a whole bunch of topics, so expect a steady stream of blogs over the next couple of months. First up was an update from Pete Hardee (Director of Product Management) on, surprise, surprise, formal verification. I’m always trying to learn more about this space, so I picked a couple… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 2 of 2)

The second panel is about system coverage and big data. Coverage metrics have been used to gauge the quality of verification efforts during development. At system level, there are still no standardized metrics to measure full coverage. The emergence of PSS, better formal verification, enhanced emulation and prototyping techniques… Read More

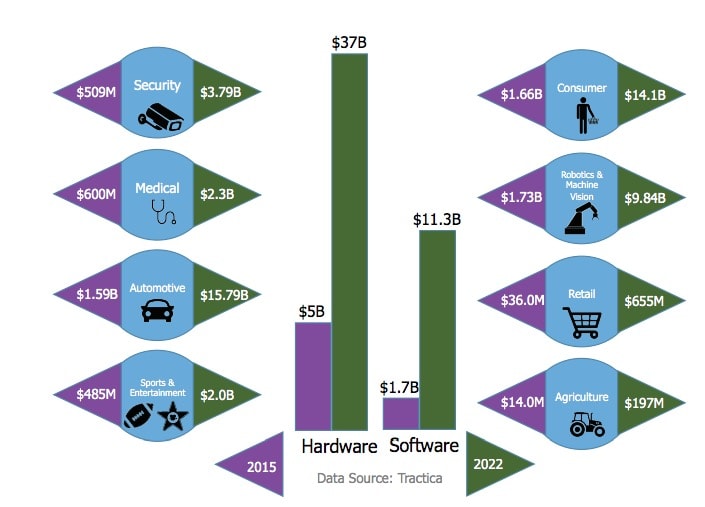

Computer Vision and High-Level Synthesis

Computer vision as a research topic has been around since the 1960’s and we are enjoying the benefits of this work in modern-day products all around us as robots with computer vision are performing an increasing number of tasks, even our farmers are using computer vision systems to become more productive:

- AgEagle® has a drone

CEO Interview: Ramy Iskander of Intento Design

One of the more interesting parts of blogging for SemiWiki is getting to know emerging EDA and IP companies from around the world. As I have mentioned before, there are some incredibly intelligent people in the fabless semiconductor ecosystem solving very complex problems. It is a two way exchange of course since we know the market… Read More

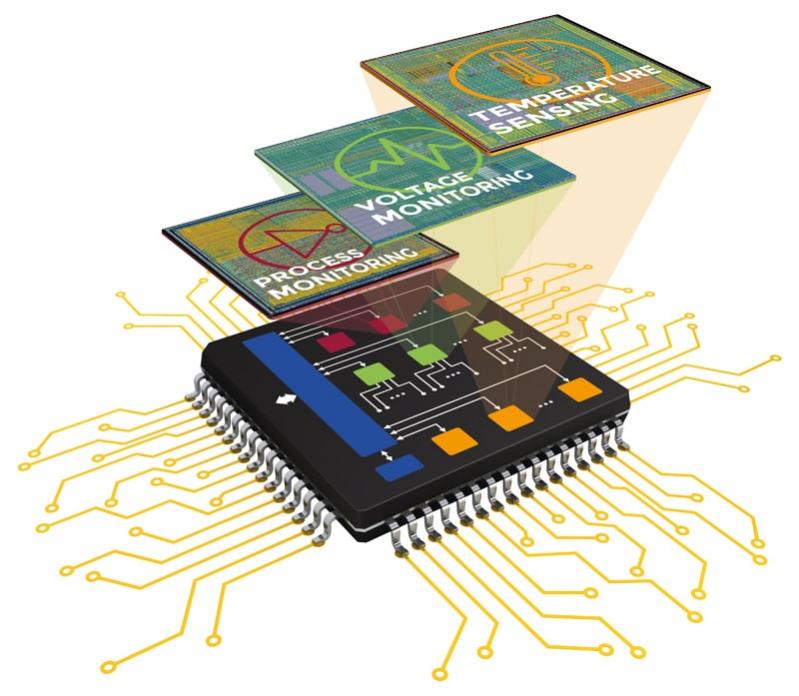

Webinar Alert – Embedded Monitoring of Process and Voltage in SoCs

In the old days to learn about new semiconductor IP you would have to schedule a sales call, listen to the pitch, then decide if the IP was promising or not. Today we have webinars which offer a lot less drama than a sales call, plus you get to ask your questions by typing away at the comfort of your desk, hopefully wearing headphones as … Read More

Another Application of Automated RTL Editing

DeFacto and their STAR technology are already quite well known among those who want to procedurally apply edits to system-level RTL. I’m not talking here about the kind of edits you would make with your standard edit tools. Rather these are the more convoluted sort of changes you might attempt with Perl (or perhaps Python these days).… Read More

Solving the EDA tool fragmentation crisis