Modern SoCs can be complex with hundreds to thousands of IP blocks, so there’s an increasing need to have a front-end build and assembly methodology in place, eliminating manual steps and error-prone approaches. I’ve been writing about an EDA company that focuses on this area for design automation, Defacto Technologies, and we met by video to get an update on their latest release of SoC Compiler, v11.

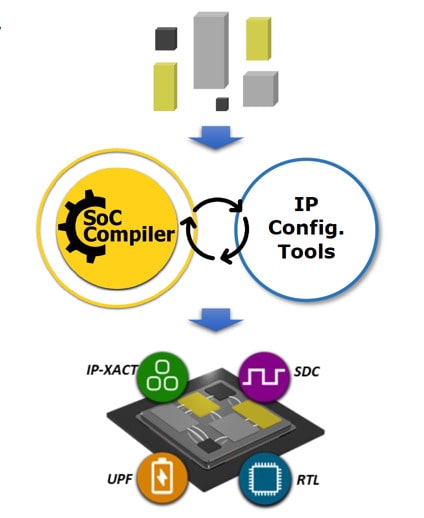

With SoC Compiler an architect or RTL designer can integrate all of their IP, auto-connect some blocks, define which blocks should be connected, and create a database for simulation and logic synthesis tools. Both the top-level and subsystems can be built, or you can easily restructure your design before sending it to synthesis. Using SoC Compiler ensures that design collaterals such as UPF, SDC and IP-XACT are coherent with RTL. Here’s what the design flow looks like with SoC Compiler.

Another use of the Defacto tool is when physical implementation needs to be linked to RTL pre-synthesis. More precisely, when Place and Route of all the IP blocks isn’t fitting within the area goal, you capture the back-end requirements and create a physically-aware RTL to improve the PPA during synthesis, as the tool also has power and clock domain awareness. When building an SoC it’s important to keep all of the formats coherent: IP-XACT, SDC, UPF, RTL. Using a tool to keep coherence saves time by avoiding manual mistakes and miscommunications.

In the new v11 release there has been a huge improvement in runtime performance, where customers report seeing an 80X speed-up to generate new configurations. This dramatic speed improvement means that you can try out several configurations per day, resulting in faster time to reach PPA goals. What used to take 3-4 hours to run, now takes just minutes.

One customer of Defacto had an SoC design with 925 IP blocks, consisting of 4,900 instances, 5k bus interface connections, and 65k ad hoc connections, where the runtime to make a complete integration completed in under just one hour.

V11 includes IP-XACT support and management of: TGI, Vendor Extensions, multi-view. The latest UPF 3.1 is supported. Improvements to IP-XACT include support of parameterized add_connection, and Insert IP-XACT Bus Interface (IIBI).

There’s even some new AI-based features that improve tool usability and code generation tasks. You can use your own LLM or engines, and there’s no requirements to train the AI features.

Users of SoC Compiler can run the tool from the command line, GUI, or even use an API in Tcl, Python or C++ code. Defacto has seen customers use their tool in diverse application areas: HPC, security, automotive, IoT, AI. The more IP blocks in your SoC project, the larger the benefits of using SoC Compiler are. Take any existing EDA tool flow and add in the Defacto tool to get more productive.

Summary

During the past 17 years the engineering team at Defacto has released 11 versions of the SoC Compiler tool to help system architects, RTL designers and DV teams become more efficient during the chip assembly process. I plan to visit Defacto at DAC in booth 1527 on Monday, June 23 to hear more from a customer presentation about using v11.

Related Blogs

- 2025 Outlook with Dr. Chouki Aktouf of Defacto

- Build a 100% Python-based Design environment for Large SoC Designs

- Defacto Technologies and ARM, Joint SoC Flow at #61DAC

- A Joint Solution Toward SoC Design “Exploration and Integration” released by Defacto #61DAC

Comments

There are no comments yet.

You must register or log in to view/post comments.