The theme of this year CDNLive Silicon Valley keynote given by Cadence CEO, Lip-Bu Tan evolves around data and how it drives Cadence to make a transition from System Design Enablement (SDE) to Data Driven Enablement (DDE). Before elaborating further, he noted on some CDNLive conference statistics: 120 sessions, 84% done by users, 1200 registered attendees and for the first time it was extended to a two-day event.

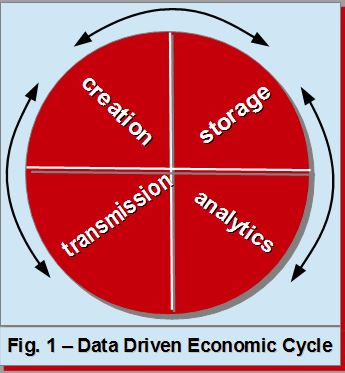

Lip-Bu provided snapshots of data growth hitting 5-8 Zettabytes volume. He indicated that in data driven economic cycle, we need to understand and address how data get created, stored, transmitted and analyzed as illustrated in figure 1.

Admitting to have more financially apt perspectives, Lip-Bu shared his upbeat take on how data has driven the economic cycle. Last year growth was 22% and for the first time crossing the $400 billion mark. He noted it has shown an encouraging strength going forward. The enablers, he coined as ‘key waves’ are in mobile, automotive, machine learning, edge computing and data center.

For 2018-2019, these segments will bring in growth ranging from 4.2% CAGR in cellular (5G, 3D sensing), 11.4% CAGR in automotive (ADAS, infotainment, etc.) to 13.1% CAGR in IoT (with distributed edge clouds, closer to user, shorter latency and different way to compute). He also reiterated growth coming from hyperscale webservices or data centers. He shared research data on AI related Venture Capital (VC) funding to top $14 billion with 1600 deals and 42% projected CAGR for Deep Learning chipset covering 2016 – 2025 period.

The opportunities are there, spanning from sensors and devices feeding data to the intelligent edge (where protocol translation and device management take place), through ML and neuromorphicprocess, and eventually ending with the cloud. On the horizon, Lip-Bu pointed out some emerging disruptive technologies such as silicon photonics, neuromorphic computing, quantum computing, nanotubes, and blockchain as becoming the future growth drivers. There will be push towards 400Gb/s and 800Gb/s interface speeds; augmenting quantum with AI to gain stability and performance; neuromorphic applications with ultra-low-power environment; blockchain assisted transaction through semi/GPU’s and brain related applications (wakeup or sleep controls).

AI and Hardware Design

Halfway into his presentation, Lip-Bu introduced two guest speakers addressing hardware solutions optimized for machine learning related and data analytics applications. The first one was Rodrigo Liang, a former Oracle SPARC hardware executive turned CEO, who just received first round of funding for his SambaNova System startup. “Semi(conductor) is capital intensive effort”, he said. He believed semiconductor (silicon) is in the center of AI. “We need to consider the software stack, what the software wants”.

Rodrigo replayed the compute evolution from scale-up in nature, to scale-out and eventually to AI computing oriented. Each domain owns its own unique bottleneck to tackle: from CPU instruction set, network latency or bandwidth to the current memory bandwidth or capacity related. Furthermore, each is also characterized by its own business challenges (such as power, cooling, cost constraints) and technology issues (memory, implementation platform: FPGA vs custom ASIC, new software development: neural network types).

The second guest speaker was Gopal Raghavan, CEO from Eta Compute, a startup founded in 2015 attempting to deliver enabling solution for intelligent IoT devices. He showcased an embedded platform to do low-power, machine learning audio/speech and visual/image recognitions, allowing training done on the edge. This approach was intended to avoid the need of transmitting high volume data over the power intensive RF based network.

The hardware design was asynchronous and utilized a few of Cadence tools (JasperGold formal verification, Modus test insertion, Virtuoso ADE, Variety and Tempus Statistical). The amount power consumed by the demonstrated device was between 1.0 to 1.5 mW and only needing 55nm low-cost, process technology.

Enabling Cadence Solution Offering

In the second half of his talk, Lip-Bu showed more growth data in design starts based on technology nodes, including for 10nm and smaller of 29.2%. The projected EDA CAGR growth of 6.2% for 2017-2022 (from 2.1% level in 2011-2016). He noted that as proof to Cadence’s culture of innovation, between 2015-2017 more than 25 new organically developed tools were introduced. He stressed on three areas in moving from SDE to DDE, namely system integration, package and board and CHIP (core EDA).

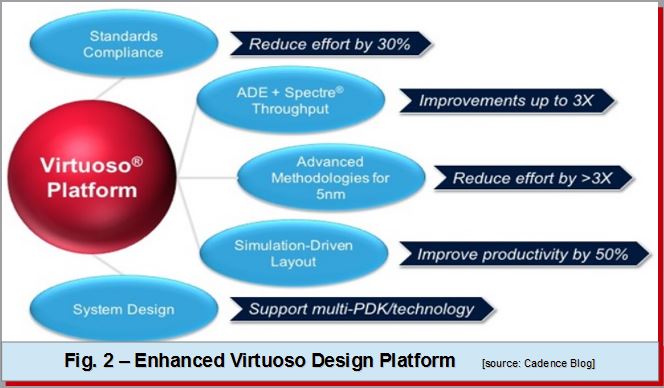

He announced an enhanced Virtuoso Design Platform to support advanced process nodes including 5nm (more coverage on this in my subsequent blog). He highlighted solution supports to photonics (hi-speed) or packaging (2.5D, 3D); the ongoing AI/ML augmentation in the implementation fabrics (from design creation, physical implementation, electrical signoff to physical signoff; and addressing mixed-signal, low-power and safety in verification spectrum (from formal/static, simulation, emulation to prototyping). His take on key technologies to address the uncertainty of design intent are parallelization, optimization and ML or data analytics.

Closer to the design ecosystem, the IP segment has an 18% growth and tends to be more vertical focus (HPC, auto, mobile/communication). It has a comprehensive portfolio including for advanced nodes with further works in PCIe, USB and memory related areas. Commenting on the recent nuSemi acquisition as enabling those hyperscale data center to address high-speed I/O connectivity needs, he alluded to the Star-IP notion as applied to Tensilica. He said Tensilica processor as an ideal core to power various kind of applications such as upcoming sentiment analysis, song analysis, etc. Its accompanied software stack includes Xtensa Neural Network Compiler on top of Xtensa C/C++ compiler.

In his closing remarks, Lip-Bu convinced that the existing design ecosystem comprising of four spheres (foundry, IP, EDA/Cadence, customer) should now include these additional, smaller spheres (software, channel, standard and compliance, design tools). It is a $400 billions IT industry with new frontier of requirements. “It is not a sunset industry”, he quipped.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.