In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big questions on their mind:

- Is first silicon working?

- Do we have any functional bugs?

- Do we have any test program bugs?

Getting time on an ATE system is a big challenge, because these specialized testers can be pre-booked for other devices and you may just have to wait for your turn to open up in the schedule. Let’s take a look of the silicon bring-up process:

- DFT engineers create ATPG patterns

- ATPG patterns converted into tester-specific format

- Test program runs on the ATE system

- STDF output file gets translated into failure date

- Identify failing logic

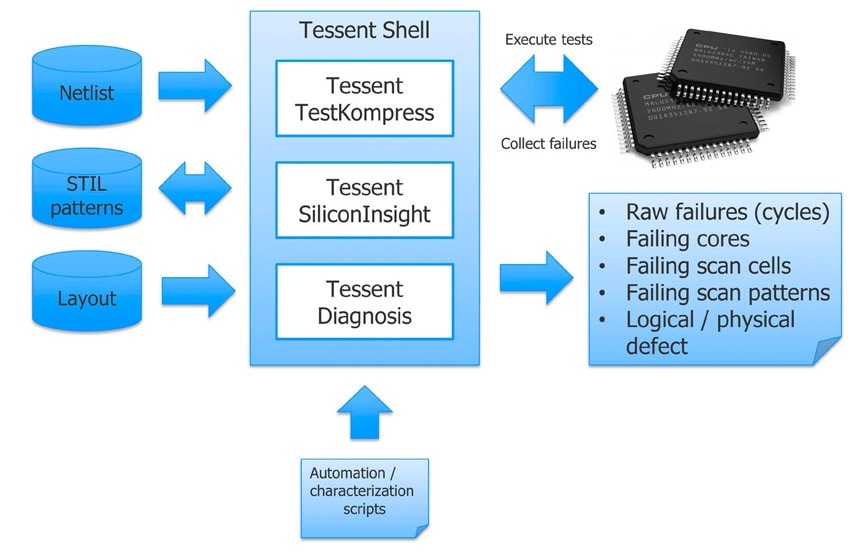

Here’s a flow-diagram of silicon bring-up and debug:

![]()

Another complexity is that your ATPG patterns can be generated at the core level, but then need to be re-targeted to the chip-level. If so, then the failure date needs to be reverse mapped from chip-level to core-level prior to any diagnosis. This flow is complex, takes precious time and can be prone to mistakes.

See how there can be drama between test engineers and DFT engineers, getting time on the tester, or even diagnosing failures between core and chip levels?

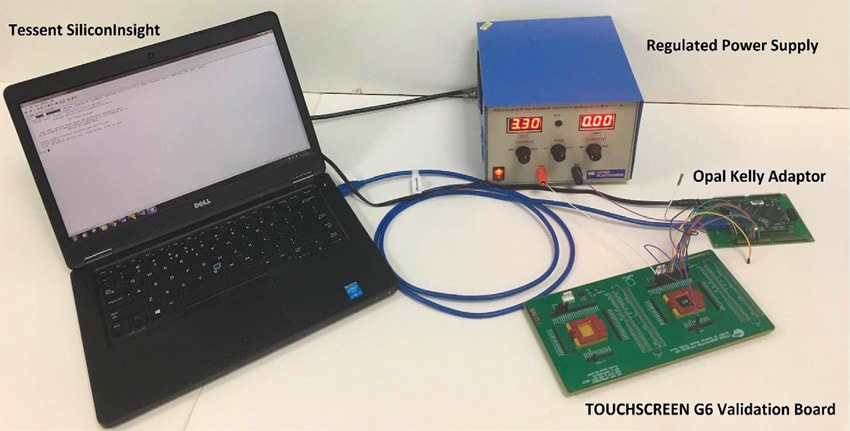

There is a natural back and forth between test engineers and DFT engineer during silicon bring-up, so anything to help communicate or cut time in the debug process is certainly welcomed. Mentor did something about improving this situation by creating a new bring-up flow called the Tessent SiliconInsight Desktop flow, and here’s what their setup looks like:

![]()

With this approach a DFT engineer can do silicon bring-up using the Tessent Shell environment connected to simple test instruments, USB to digital adaptor and a validation board. Even the test engineers can use this same setup instead of relying upon a complete ATE system. Nobody has to wait for scheduling time on the ATE when using this desktop flow instead. Failure data is readily understandable with the desktop flow using either non-compressed or compressed ATPG patterns, so there’s no long cycles of pattern execution and analysis.

Alternatively you could try a simple JTAG port approach to silicon bring-up, but then you wouldn’t have the flexibility of SiliconInsight Desktop because with it’s non-JTAG test access it can support ATPG patterns with chip compression and more than 25 external scan channels for test and diagnosis. Yes, there is some engineering effort for your team to create the validation board, but it’s a convenient way to allow control of your DUT with simple instruments.

On the software side here’s how you create your tests and diagnose results during bring-up:

Using this flow during silicon bring-up a failure occurs in a test pattern and you want to know which specific scan cells find the failure. If your chip is using on-chip compression and hierarchical DFT then it calls for some sophisticated decoding and dedicated diagnosis patterns. Fortunately for us when using Tessent SiliconInsight all of those details are automated, so we can focus on the analysis part.

Case Study

Cypress Semiconductor shared their actual experience during bring-up of a touchscreen controller chip at the IEEE%20International%20Workshop%20on%20Defects,%20Adaptive%20Test,%20Yield%20and%20Data%20Analysis%20-%20Call%20for%20participation.eml.html”]2016 IEEE Workshop on Defects, Adaptive Test, Yield and Data Analysis. Here’s their setup using Tessent SiliconInsight:

When ATPG patterns were run then a failing cycle was found, and diagnosis pinpointed the suspects as two flops in a scan chain. The engineer was then able to isolate and mask the failing flops, and create a new ATPG pattern set. With the new pattern set the tests passed with no other failures detected. They found the root cause of the silicon failure with this new bring-up flow, all without having to use a costly ATE system and in a much shorter time frame than before.

Conclusion

Silicon bring-up is filled with anguish, pain and pressure, as everyone in the company wants to know how healthy first silicon is looking. Using a new approach called Tessent SiliconInsight Desktop looks to be quite promising because it only requires simple instrumentation, laptop, adapter board and a verification board. Your expensive ATE systems can be used for production requirements, instead of silicon bring-up now. This new flow supports lots of features:

- Embedded memories

- Logic

- IEEE 1687 IJTAG instruments

- Quick failure mapping

- Diagnose to failing memory cell, scan cell or net segment

Read the complete six page White Paper online.

Related Blogs

- Mentor Tessent MissionMode Provides Runtime DFT for Self-Correcting Automotive ICs

- Mentor Tessent Products Ready for Second Edition of ISO 26262 Coming in March 2018

Comments

One Reply to “The Pain of Test Pattern Bring-up for First Silicon Debug”

You must register or log in to view/post comments.