This builds on a couple of topics I have covered for quite a while from an analysis point of view – integrity and reliability. The power distribution network and some other networks like clock trees are particularly susceptible to both IR-drop and electromigration (EM) problems. The first can lead to intermittent timing failures, the second to permanent damage to the circuit. There are a number of products to support analysis for power integrity and EM risks, but then what? You need to modify your design to mitigate those risks; the analysis tools won’t do that for you.

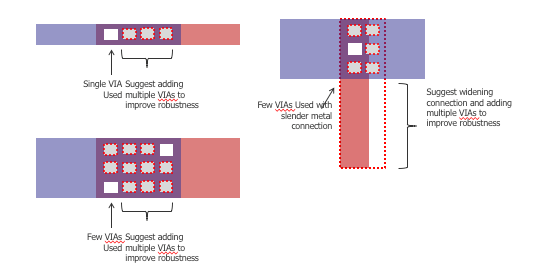

In both cases the fix is to reduce resistance in the relevant part of the network. Within a layer you can widen the interconnect but at points where the network crosses between layers, you need to add more vias (or via stacks) – more points of contact between layers → lower resistance → lower IR-drop and EM. But this is a very design, location and use-case-specific optimization not commonly found in implementation build tools, so implementation teams have often built their own Calibre-based applications to handle adding these vias.

Providing the ability to create your own apps is part of the value-add of the Calibre family, particularly through PERC (programmable electrical rule-check), which provides the infrastructure to scan the design to find named nets and where these cross between layers, flagging where vias must be added. The more sophisticated teams have probably also automated, to some level, adding those vias, perhaps through Calibre-YieldEnhancer.

But as always there’s a challenge. When processes were simpler, adding vias was relatively straightforward, but in advanced processes (e.g. 7nm) ensuring DRC and LVS correctness in changes becomes a lot more complex. Managing this complexity has become an iterative flow: automate via additions as well as you can, re-run DRC and LVS, then fix violations as required. Do-able but this can become very painful when you may need to implement changes at many nodes across large networks (such as in a power distribution network).

Of course a better way would be to make the edits correct by construction but that requires a very good understanding of the process and of course the tools. The Calibre team already has an app, PowerVia, to do this and have partnered with GLOBALFOUNDRIES to add rules in support of their GF7LP process (GF have plans to extend it to other processes), a capability which is now a part of their Manufacturing Analysis and Scoring (MASplus) and which they presented at the recent Mentor U2U user-group conference.

Analysis starts with target nets for enhancement – ports (like power and ground nets) and other user-selected nets. The flow uses PERC to identify nets not already labeled in the layout, along with where those nets cross layers, then YieldEnhancer/PowerVia adds DRC/LVS clean vias at those intersections to the extent they can be added (it will not remove existing user/tool-added vias). The GF flow adds as many vias as possible (consistent with not increasing area) at each of these intersections. I would guess the reasoning is that even if this might be overkill in some cases, when it comes to reliability overkill is not so bad.

How big a deal is this? GF showed benchmark info in which they boosted vias up to 120% over the starting point and the design was DRC/LVS clean, so no need for iteration. That’s a lot of vias if you had to add them manually, and still a lot of work if you had to iterate DRC/LVS following less than perfect fixes. The GF speaker (Nishant Shah) added a few more details in Q&A. The flow is GDS-based, so should be thought of today as a finishing step, not designed to take back (yet) to P&R. The app requires you to define which nets to address, though it will assume port nets by default. And the flow is designed primarily to address IR-drop and EM on high current-density nets. GF handles via-doubling for reliability in other nets in a different flow.

In discussion with Jeff Wilson (Director of Marketing for the DFM solution in Calibre) and Matt Hogan (PMM for Calibre design solutions), their enthusiasm for this type of solution – foundry-based apps on top of Calibre – was clear. They see design companies struggling to handle the workload added by these kinds of reliability enhancements. While they can script these solutions themselves using PERC and YieldEnhancer, the effort required from implementation and CAD teams – to develop and prove out scripts and to iterate to get to DRC/LVS clean – is becoming intolerable. A better solution is a foundry-sponsored app, building on the same platform, allowing for designer control on which nets to address, and then automating fixes correct by construction in one pass.

For more information on Calibre YieldEnhancer and Calibre PERC (where they handle a lot of other interesting checks – ESD, EOS, voltage-dependent DRC rules for multi-power/voltage domains and more), stop by Mentor’s DAC booth (#2621) June 25-28. You can view a full list of their booth and conference sessions HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.