It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier along with the functional verification of the SoC. Today, an SoC is a complete system with various functional units with different power profiles and requirements. Hence the traditional method of running simulation, generating switching activity for a number of cycles, using a power analysis tool to analyze this activity, and then extrapolating to estimate power for the whole SoC is no more appropriate; it was fine for smaller chips with limited functionalities. Today, we need to analyze actual switching activity for the complete run of applications on an SoC.

Emulation is an emerging solution to capture switching activity over long emulation run; typically in an SAIF (Switching Activity Interchange Format) file. However SAIF do not have temporal information which is a key need to identify power peaks at different times. VCD and FSDB formats have temporal information; however they are inefficient due to their large generation time and then read/write times. Also, there are other inefficiencies in their data organization and storage and access mechanisms. Moreover, the power analysis tools may not be able to handle such large files generated by emulation. Overall, even an emulation methodology based on file-based flow is not the right solution for exploring and analyzing power at the SoC level.

So, what’s the alternative for detailed power analysis of design regions and applications that cause high switching in SoCs in real scenarios? During 52[SUP]nd[/SUP] DAC we heard from Mentorand ANSYSabout an innovative approach where Veloce generates real-time dynamic power data and PowerArtist reads it directly for power measurement and analysis without any file-based interface. I have already written about some details on PowerArtist side; see the link at the end of this article. Now it’s my pleasure to write about some actual details of what happens on Veloce side.

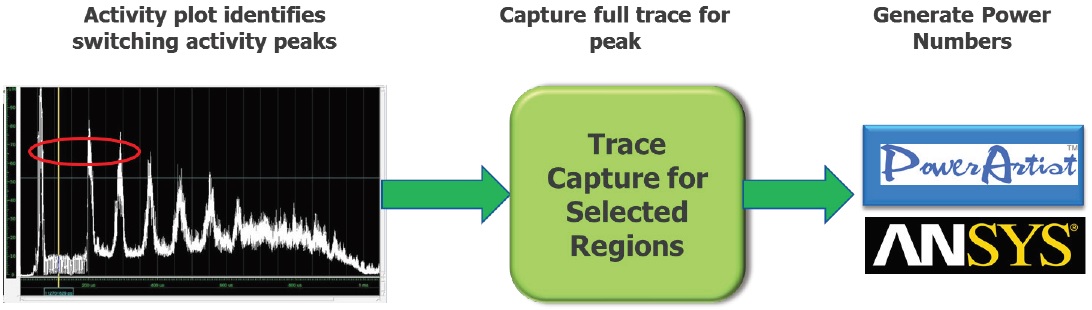

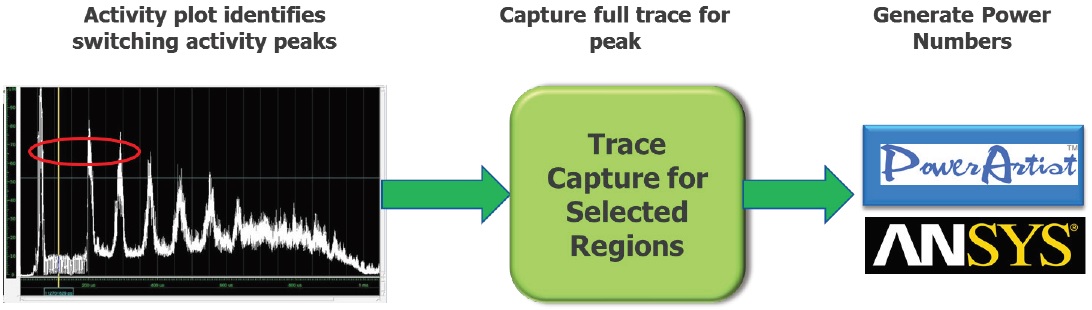

Veloce emulation system is used to boot the OS and run live applications. The Veloce Activity Plot is its unique capability to identify high switching regions over long emulation runs and enable designers to trace back to the logic blocks or applications that have power concerns. One can view the activity plot of a full design and analyze its power consumption pattern in an order of magnitude lesser time than the time taken in a file-based system. As an example, the activity plot of a 100 million gate design for 75 million clock cycles can be generated in just 15 minutes by Veloce emulation system.

After identifying high switching activity regions at the top level of the design, the sub-blocks or applications responsible for high switching activity can be analyzed further. The time zone information thus obtained can be captured in a tzf (Time Zone File) file and sent to Veloce for generation of complete data for the selected time windows for detailed power analysis.

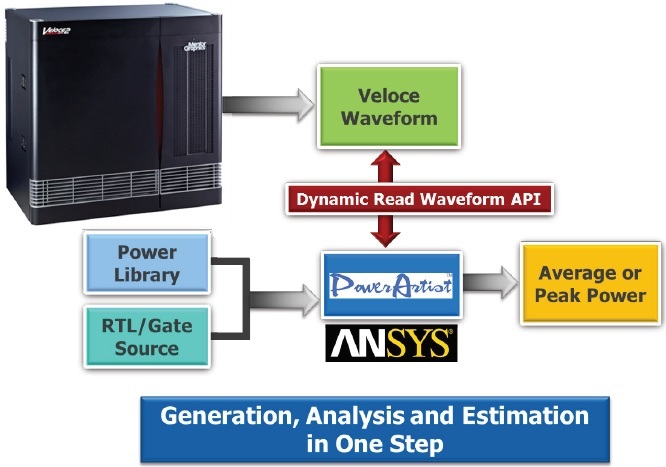

During the emulation run, live switching data can be sent to PowerArtist through Dynamic Read Waveform API (DRW-API). This approach enables accurate power calculation at the system level where booting an OS and running software applications is required. The dynamic API-based streaming of switching data between emulation and power analysis tools allows for all operations to be run in parallel including emulation of the SoC, capture of switching data, reading of the switching data, power analysis and generation of power numbers.

Both the tools work on the same data model which improves the efficiency of data exchange between them. The compile times of both tools are aligned. Also, a native ‘critical signal list’ (typically 10-20% of total signals in a design) is used to further improve time to power performance by reducing data exchange between the tools.

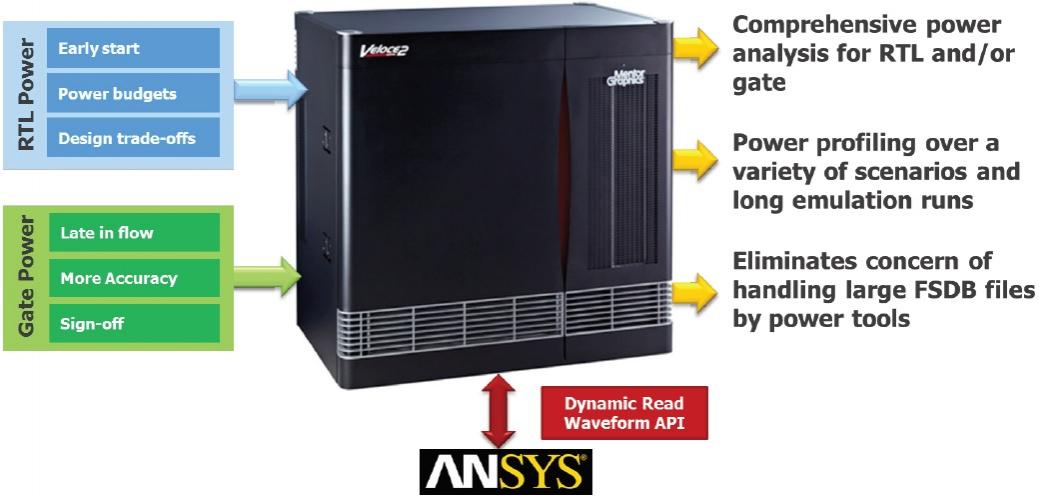

Veloce along with PowerArtist enables a complete RTL power exploration for power budgeting and tradeoffs, as well as an accurate power analysis and signoff at the gate level in a targeted application environment. The direct data exchange provides huge improvement in the time of overall flow. The verification cycles to collect design switching activity can be very long compared to simulation. Data-driven decisions for accurate power analysis are enabled over a variety of test scenarios.

This particular flow to generate power numbers has provided up to 4.25x speed improvement over file-based flow on real customer designs. A table of designs along with their speed improvement numbers is given in a whitepaper written by Vijay Chobisa and Gaurav Saharawat at Mentor Graphics. The whitepaper contains more details about the new methodology; it can be accessed from HERE.

Also read: How PowerArtist Interfaces with Emulators

This innovative methodology unfolds a powerful, accurate, and right way of power measurement and analysis in a new environment where multiple functions such as computing, gaming, video streaming, watching movies etc. can be integrated on a single device such as a Smartphone. We can expect more such innovations for power analysis in the near future.

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

Comments

0 Replies to “Power Analysis Needs Shift in Methodology”

You must register or log in to view/post comments.