Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies. Test benches are as old as the earliest designs. The advent of language based design created an opportunity to insert code for functional checks right into the designs themselves. But this activity was initially an informal and inconsistent practice.

In the last decade the formalization and standardization of these assertion based checks has made them easier to implement and more effective as debugging and verification tools. Accellerahas developed the Property Specification Language (PSL) for specifying assertions for a variety of HDL’s. Also, there is System Verilog Assertion (SVA) which is part of System Verilog. Both are IEEE standards.

Assertion based verification (ABV) brings with it many benefits. For one, as developers write HDL code they can add assertion checks in situ. The assertion checks added at this point can also help serve as documentation, and they will be more efficient and potentially more complete than directed and constrained random verification. Of course ABV code can be added externally as well by using the “bind” feature. In some cases that is preferable because it makes the verification code reusable, and the verification team can easily work in parallel with designers during development.

At higher levels of design abstraction ABV suites facilitate reuse. Having a set of assertion based checks for SOC building blocks makes it easier to confidently reuse blocks from internal or external sources. And this goes with knowledge that the blocks will more easily meet verification requirements. It turns out that there is now a niche market that provides Verification IP (VIP) for this very purpose. For example companies such as Mentor have large libraries of VIP for many different standard design elements. Because of their large user base and productized development, commercially available VIP can be better tested and documented than in-house developed VIP.

Performing assertion based checks with a software based simulator affords complete visibility, which is invaluable for debugging. Also it is easy to toggle on or off each level of checks: internal, block, signal, protocol, or chip level. Lastly error reporting is of a very high quality – including coverage information and data useful for debugging. Naturally this is a fully developed approach. Its main drawback is that as the verification problem moves up the hierarchy the simulation data set grows rapidly, so performance and throughput become limiting factors. Compromises on the number of clock cycles that can be run or the amount of test case data processed are necessary. Given that the verification team is always in a race with time, software based approaches alone may not suffice.

In the worst case scenario a test chip might come back with an issue that only shows up after many clock cycles or that is very data dependent. Despite high clocks rates, debugging in silicon is hindered by lack of observability. Unless critical signals or registers can be probed, tracking down problems can become an open ended task.

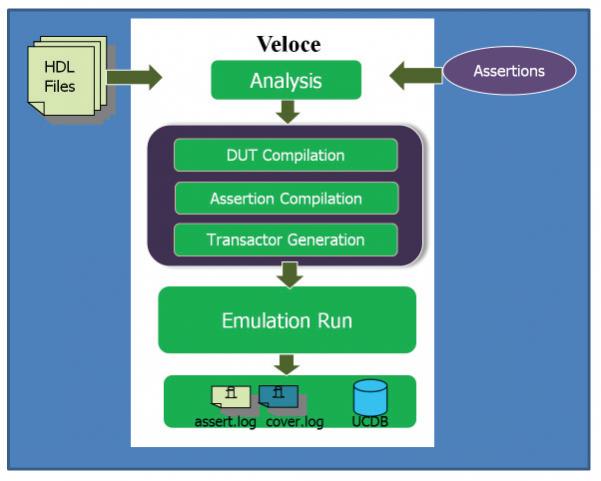

What if there was a solution that supports large design size, fast execution, high design visibility and full support for the assertion based verification standards? Mentorrecently put out a white paper that talks about using their Veloce emulators as the vehicle for performing ABV. Using an emulator can provide a huge speed advantage. Tests can be run on more cases over more clock cycles. By fully supporting the assertion based verification standards in the Veloce compilers, Mentor is making it easy to bring assertion checking to emulator users. Another big advantage of this approach is that visibility into the design is maintained so coverage data and debugging information is readily available.

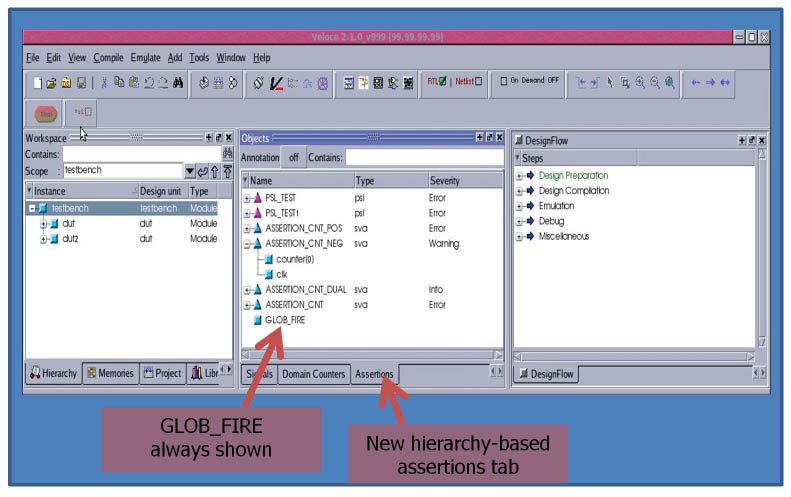

Mentor also reports that they are offering tight integration in the Veloce GUI for reporting and controlling what assertions are exercised. This allows for focused verification as the design moves from block to system level.

It is clear that combining the acceleration and flexibility of emulation with the power of assertion based verification creates synergistic effect that can boost design debug and product verification.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.