Formal verification methods are being adopted at a fast pace as a complement to traditional verification methods like functional simulation for IP blocks in SoC designs. I had a video meeting with Max Birtel, co-founder of LUBIS EDA and learned more about their history, products and vision. This company started recently in 2020… Read More

Tag: sva

Can We Auto-Generate Complete RTL, SVA, UVM Testbench, C/C++ Driver Code, and Documentation for Entire IP Blocks?

Whether it is fully autonomous driving, or wrinkle-free fabric, or ambient energy harvesting for powering electronic devices, each industry is chasing after its respective ultimate goal. For the semiconductor design industry, its goal is the capability to generate complete chip or IP in executable format from a high-level… Read More

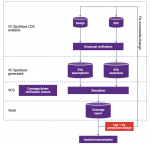

What’s New in CDC Analysis?

Synopsys just released a white paper, a backgrounder on CDC. You’ve read enough of what I’ve written on this topic that I don’t need to re-tread that path. However, this is tech so there’s always something new to talk about. This time I’ll cover a Synopsys survey update on numbers of clock domains in designs, also an update on ways to… Read More

Next Generation Formal Technology to Boost Verification

With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More

A Comprehensive Automated Assertion Based Verification

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More

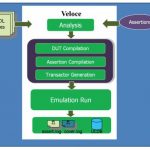

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

SpyGlass CDC: A Comprehensive solution for addressing CDC issues

About a decade ago, semiconductor designs had just a few asynchronous clocks which were easily managed by designers through the process of manual design reviews. The situation today is completely different. An SoC can have hundreds of asynchronous clocks, driving different complex functions, spread across various IPs, supplied… Read More