I’ve watched the SPICE market segment into multiple approaches, like: Classic SPICE, Parallel SPICE, FastSPICE and Analog FastSPICE. In a similar fashion the same thing just happened to EM/IR analysis, because after years of waiting we finally have a different approach to EM/IR analysis that works at the top-level of an IC that I’m calling Fast EM/IR analysis. I came to this conclusion after a video call with Maxim Ershov, CEO at Diakopto and Kelvin Khoo, COO at Diakopto.

EM/IR analysis has traditionally been approached at the transistor-level, or the cell-level, producing very accurate results, but at the expense of long run times as the design is assembled from sub-blocks, and then ultimately run on the top-level. The run times have got “out of control” in FinFET technologies as the size of the designs, and the number, magnitude and impact of parasitic elements have grown exponentially. As a result, it has become impractical to analyze EM/IR at the top-level because such simulations could easily take weeks.

In addition, traditional EM/IR tools are notorious for being very complicated and tedious to set up, use and interpret the results. They can also be used only very late in the design stages, when layouts are mostly complete and hard to change.

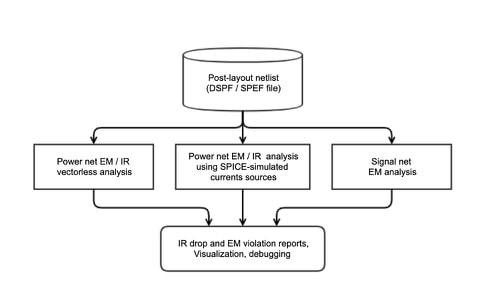

Diakopto’s PrimeX was developed in response to customers’ need for a new category of Fast EM/IR tools, that are capable of verifying top-level power nets, which is not feasible with other EM/IR tools. PrimeX delivers on this promise by trading off some accuracy for dramatic gains in speed, capacity, and ease of setup. But what makes PrimeX shine is the ease-of-use for novice users, along with insightful debugging capabilities that identify the few areas and elements (out of a sea of millions or billions) that cause EM/IR problems.

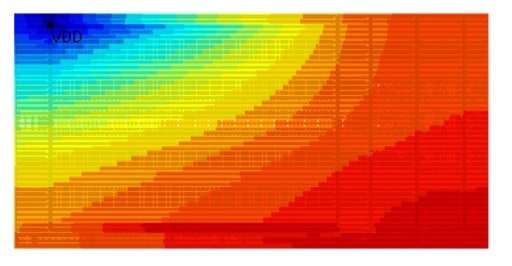

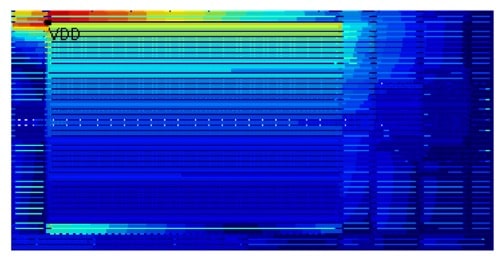

The majority of critical EM/IR problems are caused by “silly” layout mistakes, such as missing or insufficient number of vias, long narrow metal lines, cutouts in metal planes, poor connection of pad (cells) to the power nets, and insufficient number or sub-optimal placement of power switches. Design teams should not need to waste a couple of weeks by running fully accurate EM/IR analysis to detect and find these mistakes.

PrimeX enables a very fast resistance, EM and IR drop analysis, thanks to a novel “approximate computing” methodology. This “approximate computing” methodology includes a variety of different techniques, such as utilizing the design intent information, design hierarchy, simplifications using physics-based considerations.

This allows users to perform multiple quick iterations and to clean up layout mistakes early in the design phase. It also allows design teams to perform EM/IR analysis for very large power nets at the top-level in a few hours, instead of weeks, to detect the overwhelming majority of layout issues that cause EM/IR problems.

As an example, all power nets for a high-speed SerDes (112-224 Gbps) implemented in 5nm technology were analyzed in an overnight run using PrimeX.

The tool also offers powerful debugging capabilities beyond what is commonly found in traditional EM/IR tools. It provides deep insight into EM/IR problems, and reports root causes in a top-down manner: by net, by layer, power switches, and by polygon and colors over the layout.

In addition to speed and insights, PrimeX was designed from the start to be easy to use and set up. This means that it can be used by any design or layout engineer, without the need for lengthy training or for them to be experts in an EM/IR tool. In addition, PrimeX requires minimal configuration and set up, so there is no need for a dedicated expert or CAD group to bring up, maintain and support the tool and flow.

Another drawback of the traditional IC design flow is that EM/IR analysis happens quite late in the process, only after DRC/LVS for each block and for the top hierarchy level has become clean, requiring long iteration cycles, and long simulation times to get the current sources information. By this time, it is almost too late to make layout ECOs, and designers are in panic mode right before a tapeout deadline. The new methodology offered by PrimeX allows designers to analyze EM/IR earlier in the IC flow, and often prior to LVS clean, to pinpoint bottlenecks and choke points, and to clean up the design/layout much earlier.

According to Diakopto, PrimeX has been adopted by 8 customers, several of which have made the tool their sign-off flow for the top-level EM/IR verification. PrimeX builds on the success of Diakopto’s flagship product, ParagonX, which has been adopted by over 40 customers for debugging IC designs sensitive to layout parasitics.

The headquarters for Diakopto is in San Jose, a strategic location for a smaller EDA vendor to be located, because of the density of IC firms in Silicon Valley. You can run the Diakopto tools on any Linux box (CentOS or Red Hat). PrimeX runs fast enough on a single core so far, that they haven’t done much on a parallel approach, but stay tuned. One CPU is sufficient right now.

Summary

EM/IR analysis tools have been around for over two decades now, and the limitations of capacity, slow run times, and LVS clean, are well understood by users. What’s new is that Diakopto has pioneered a new approach of Fast EM/IR analysis that complements the traditional EM/IR tools, allowing the fastest results, especially at the top-level of an SoC using leading edge nodes. PrimeX is disruptive, and should be welcomed by IC design teams.

Related Blogs

Your Symmetric Layouts show Mismatches in SPICE Simulations. What’s going on?

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.