There are a few dozen causes of semiconductor failure. Most can be lumped into one of three categories: material defects, process or workmanship issues, or environmental or operational overstress. Even when all those causes are carefully mitigated, one factor is limiting reliability more as geometries shrink – and it sneaks up over time.

There are a few dozen causes of semiconductor failure. Most can be lumped into one of three categories: material defects, process or workmanship issues, or environmental or operational overstress. Even when all those causes are carefully mitigated, one factor is limiting reliability more as geometries shrink – and it sneaks up over time.

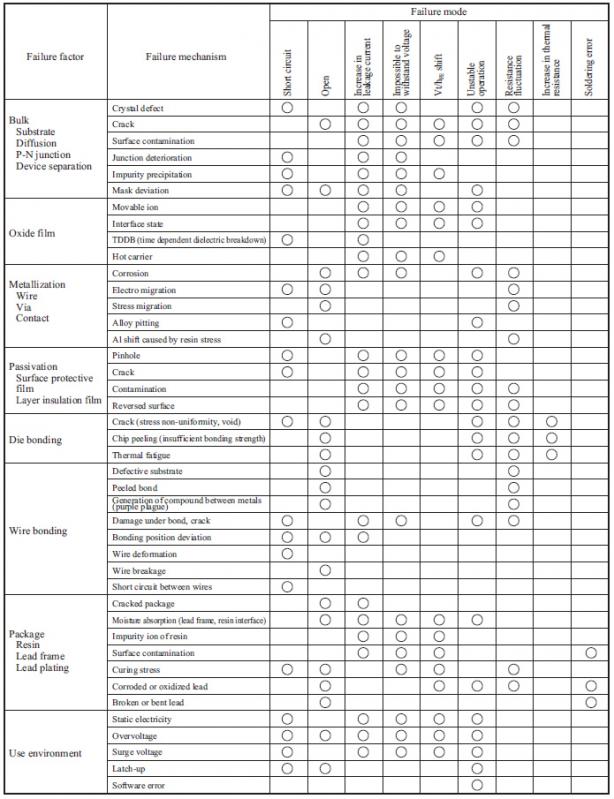

I found an interesting document from Panasonic titled “Failure Mechanism of Semiconductor Devices”, a few years old (circa 2009) but a fairly concise read and a great handy reference on defect causes. Table 3.1 from that document nicely summarizes the causes and modes of failure.

courtesy Panasonic

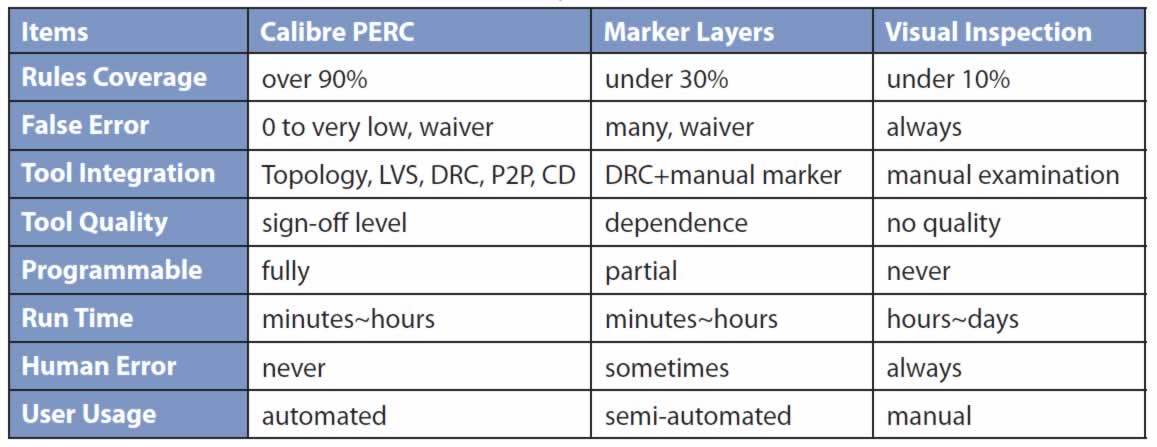

courtesy Panasonic

The first failure mode described in detail in that document is our suspect of interest: time-dependent dielectric breakdown, or TDDB. As geometries get smaller and gate oxide films get thinner, the risk of long term failure due to deterioration of the oxide film is growing. There is a gory formula expressing TDDB in terms of electric field strength, temperature, and other variables, but one sentence in the explanation draws attention:

… dielectric breakdown occurs as the time elapses even if the electric field is much lower than the dielectric breakdown withstand voltage of the oxide film.

That is a bit disconcerting, because it suggests many designs may not have accounted for or analyzed TDDB, instead proceeding on the assumption the materials in use are well within specification. To help designers improve their odds in combatting TDDB and improving reliability, Mentor Graphics has taken a new look at spacing rules with some surprising results.

As with so many design techniques for difficult-to-characterize problems, peanut butter approaches are often used to mitigate TDDB: visual inspection or marker layers, targeting congested areas thought to potentially pose a problem. The “fix” is usually extra checking as indicated, followed by applying a generous spread of spacing. By creating more separation in critical areas of a design, in effect derating the oxide material, TDDB can be forestalled.

This rather empirical, experience-based approach may have worked at less aggressive geometries with fewer power domains, but as complexity is increasing a more analytical approach is required to save EDA time and unnecessary padding that wastes valuable space in short supply. Mentor’s approach to the problem sounds simple: analyze the nets and the voltage differences between them, and apply spacing rules accordingly.

Easier said than done. An analysis like this not only has to understand the layout and power domains, but account for physical implementation details – a job normally for SPICE, but creating enough test vectors to look at all the combinations is an extremely complicated exercise. Plus, every time a design changes, the analysis has to be rerun since the prior results are basically no longer valid, and brand new problems may crop up. Did I hear someone say “more padding”?

The Mentor approach brings the capability of Calibre PERC to bear on TDDB. By performing rule-based checks on layout-related and circuit-dependent values, problem areas can be spotted quickly and accurately, without the use of marker layers or tedious SPICE simulations. With the voltage differences across the nets accurately known, rules-based spacing checks can automatically run and apply the minimum spacing needed. The savings in time, space, and false alarms compared to the peanut butter approaches can be significant according to Mentor.

Mentor’s complete white paper, authored by Matthew Hogan, describing the motivation behind voltage-aware design rule checking and its benefits in mitigating TDDB, is here:

Improve Reliability With Accurate Voltage-Aware DRC

Is TDDB sneaking up on your design, waiting to cut its life short? Did your last design take more time and use more space than it had to just to be “safe”? Has the peanut butter approach let you down lately? Calibre PERC can help replace best-guess strategies with rules-based results.

More Articles by Don Dingee…..

Share this post via:

Comments

0 Replies to “Stop TDDB from getting through peanut butter”

You must register or log in to view/post comments.