Power Management ICs are a vitally important part of system design. Evidence of this is cited by a Synopsys white paper that mentions how Apple acquired a portion of PMIC developer Dialog Semiconductor that was previously their exclusive PMIC supplier. Clearly Apple had decided that PMIC design was a strategic differentiating element of their products. PMICs play an outsized role in mobile and automotive systems. PMICs are historically analog circuits, yet now contain increasing digital content. One challenge has been to see how designers combine the need for analog power circuits with CMOS digital for control.

The Synopsys white paper, titled “Calibrate and Configure Your Power Management IC with NVM IP” written by Krishna Balachandran, Product Marketing Manager Sr. Staff, talks about the history of PMICs starting with their implementation on purely analog nodes. They discuss how the advent of BCD, which combined all the device types needed for optimal PMIC design in one technology, was a game changer. The white paper offers a good analysis of the trade-offs between BJT, MOSFET and IGBT.

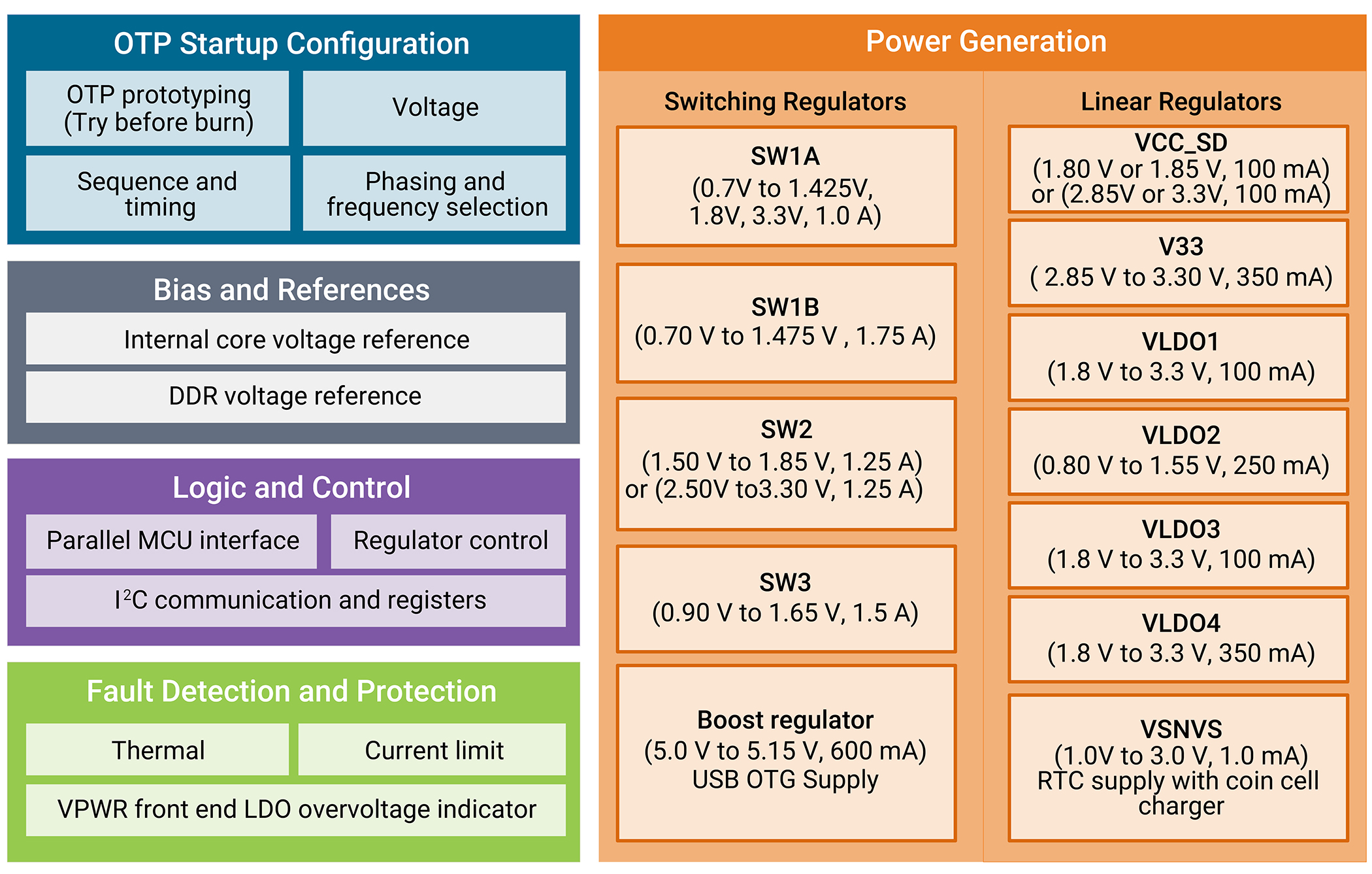

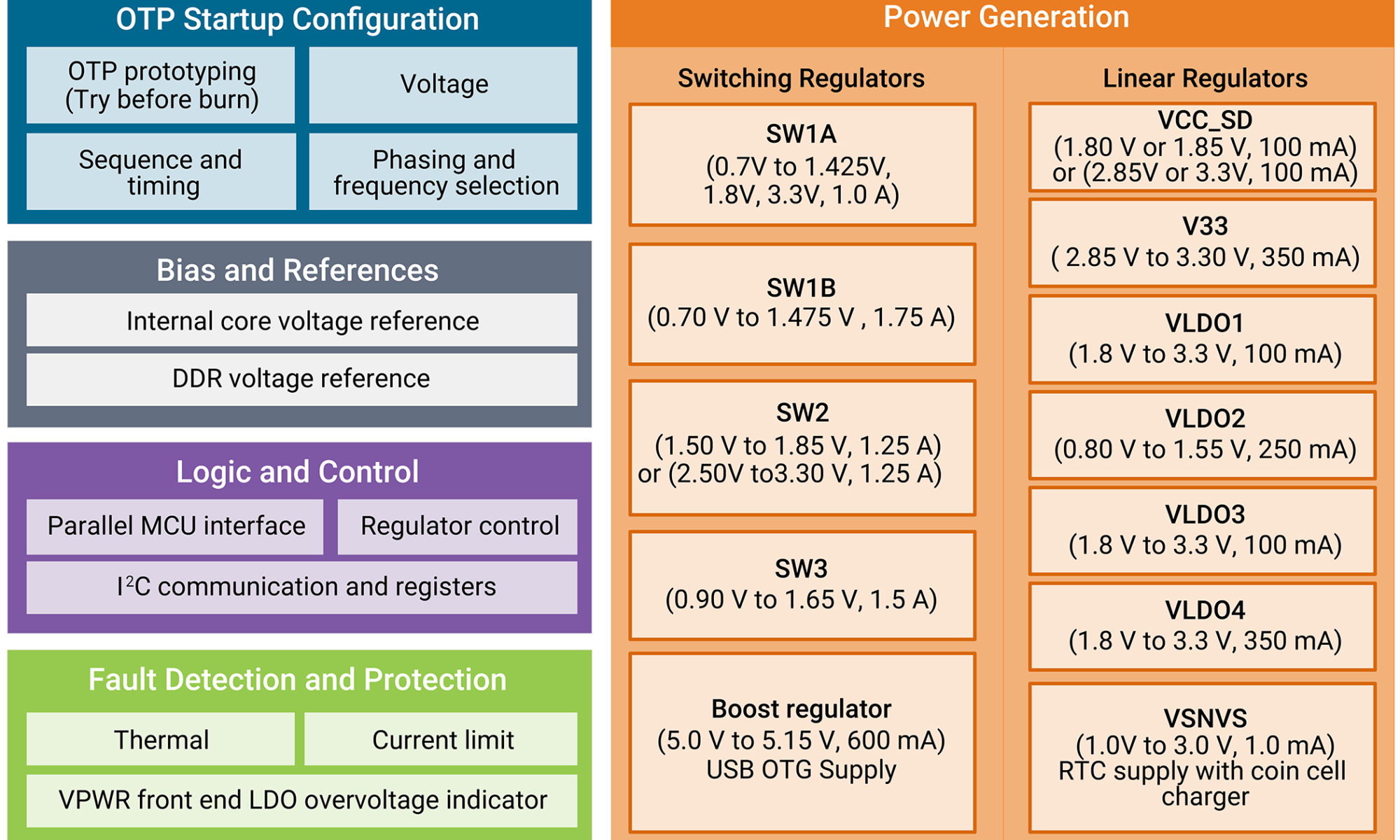

The white paper also focuses on the need to store critical calibration information and operation configuration settings using a secure and reliable method. It explores the many benefits that non-volatile memory IP offers for both the analog and digital elements in a PMIC design.

For the analog circuit there is variation from unit to unit that requires calibration and the storage of that information on the individual die. This ensures that the output meets specifications. Because many PMIC circuits are used in multiple applications, there is also a need to store configuration settings on the die as well.

One-time programmable (OTP) or multiple time programmable (MTP) Non-Volatile Memory NVM is ideally suited to the needs of PMICs. Antifuse NVM offers high compatibility with existing process mask layers by not requiring any new layers. It works with BCD or CMOS nodes with no additional process steps. Its high reliability, including operation at high temperatures makes it a good fit for automotive applications. NVM is also very compact which means that it further saves on costs.

NVM is very secure from unauthorized access and tampering. Antifuse NVM bits are not readable using scanning electron microscopes or other optical or mechanical methods. This gives them a big advantage over traditional fuse technology. Fuse technology can also develop reliability issues due to bridging from electromigration. Lastly traditional fuse technology requires a lot of area, which makes it much less cost effective.

When antifuse NVM is used it is possible to emulate MTP with OTP when sufficient storage is provisioned to allow storage of multiple copies of the data. Even though not infinitely re-writable, given reasonable estimates of lifetime rewrites, OTP can work well as a practical alternative.

The Synopsys white paper also explores the tradeoffs surrounding process selection for PMICs. While a large part of the market uses 180nm BCD, increasing digital content is encouraging a move to smaller BCD nodes. Designers also face a decision of whether to migrate to a two-die solution, with one for analog and another for digital. More complex power on and power off requirements, such as power ramping and standby modes is causing digital content to grow.

The Synopsys white paper is thorough and does a good job of articulating the issues surrounding PMIC design. PMICs are definitely a key competitive component in most systems today. Designers need to look at every opportunity to add needed features and optimize them as they reduce costs and ensure high reliability. OTP NVM technology is proving itself as a key element in this effort. The full Synopsys white paper is available here for download.

Also read:

Why It’s Critical to Design in Security Early to Protect Automotive Systems from Hackers

Identity and Data Encryption for PCIe and CXL Security

High-Performance Natural Language Processing (NLP) in Constrained Embedded Systems

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.